国产化IP创新之路(二)创新篇:突破创新及实现数据的高效传输

2022-02-28

11:57:10

来源: 互联网

点击

业界普遍预测未来的计算架构将从以处理器为中心逐渐转变成以数据为中心,内存速度和计算不再是能效瓶颈,数据移动的速度正在逐渐成为新的能效瓶颈,本篇文章将详细介绍后摩尔时代如何通过技术提升来解决瓶颈,实现数据的高效传输!

从计算为中心到数据为中心,急需突破三堵“墙”

算力墙的突破:传统处理器架构很难突破算力墙,我们需要在处理器架构创新的同时,通过各种DSA异构计算,加上现在普遍看好的Chiplet(芯粒)和先进封装等技术来突破算力墙。

◾ 处理器架构创新,多核,并行,片内异构…

◾ 各种DSA

◾ Chiplet+先进封装

内存墙的突破:目前在内存本身往更高密度和更高带宽的形态发展外,可以采用串行内存接口扩展内存,并且基于此做到内存池化,以及利用逐渐成熟的新内存介质来提升内存性能,这些相辅相成,来突破内存墙。

◾ 更高密度和更高带宽的内存

◾ 串行内存接口与内存池化

◾ 新介质内存

◾ 近存计算

IO 墙的突破:利用更高速的IO接口,更高效的传输协议以及更低的传输延时来突破IO墙。

◾ 更高速的IO接口

◾ 更高效的数据传输协议,更低的时延

◾ 在网计算

算力墙:Chiplet与D2D互联-后摩尔时代的芯片集成趋势

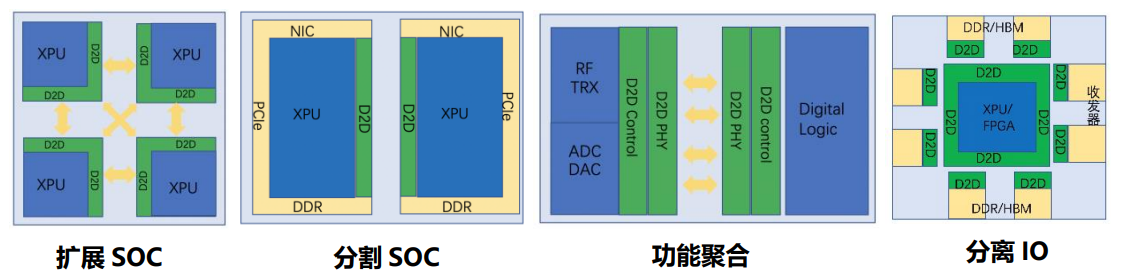

由于传统处理器架构对算力的限制,近年来采用先进封装和D2D互联的Chiplet方案流行,一方面,通过高速低延迟的D2D接口可以对所连接的SOC进行扩展/分割,另一方面,D2D可以灵活有效地实现IO口的聚合和分离,针对不同应用实现性能最优解。所以,可以预见,采用高速,低延迟,高性能的先进封装D2D互联chiplet方案正在成为后摩尔时代芯片集成趋势。

内存墙:DDR5&HBM带来高带宽、高容量,将有更广泛的应用空间

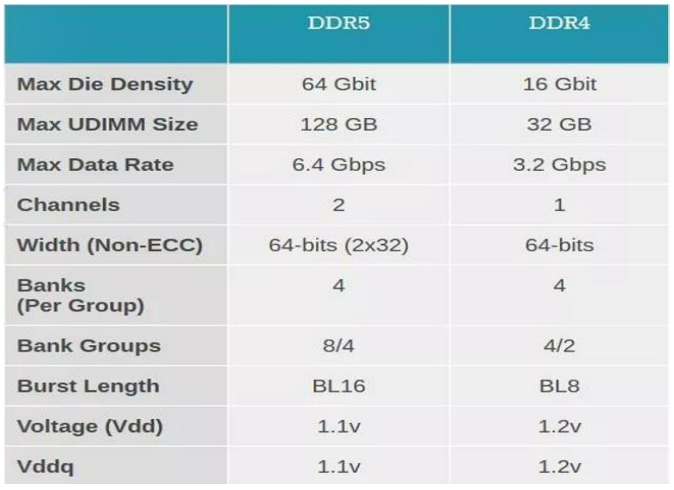

高性能计算,人工智能,以及高性能图形领域,对内存的带宽有巨大的要求,因此高带宽内存 DDR5/HBM在这个领域变得重要起来。目前在数据中心和服务器上,DDR4显得有些吃力,急需更高带宽更大容量的产品,DDR5应运而生,相比较DDR4,DDR5速率和带宽均翻倍,在功耗性能上相比于DDR4也做了大量优化。随着Intel和AMD宣布在2022年发布的下一代处理器上支持DDR5,可以预见,服务器,数据中心,和高性能计算等将在2023年大量采用DDR5以满足其对内存带宽和容量的需求。

另一种高带宽内存HBM是用空间换时间,通过堆叠,高互联密度,利用较低的频率来获得最大带宽。其最大IO速度可以到达8.4Gbps,最新一代HBM3带宽已经达到惊人的1TB/s。目前除了在一开始的GPU和后来的AI领域被应用外,HBM在CPU领域也逐渐被采用,未来HBM的应用前景将更为广阔。

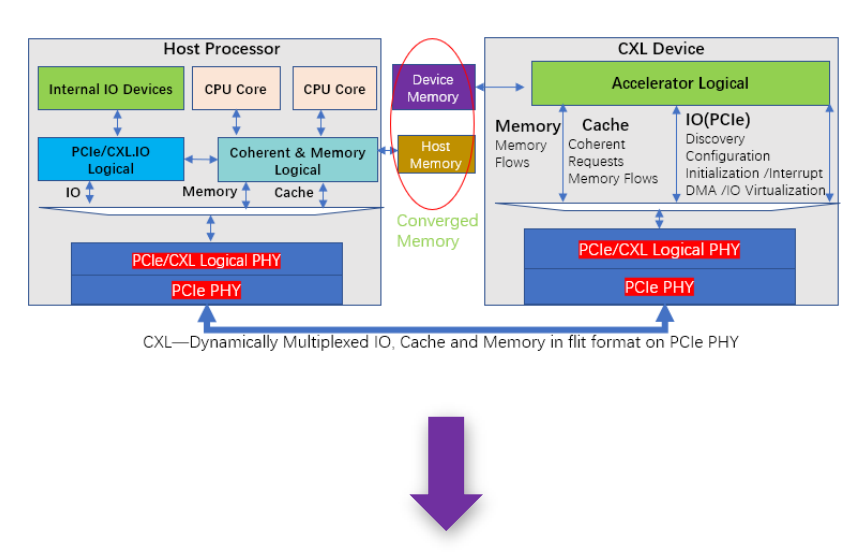

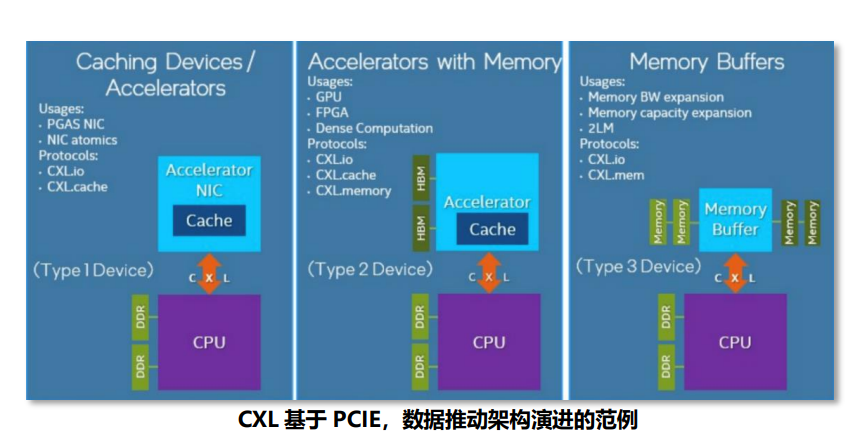

IO墙:基于PCIE的CXL带来异构计算效率变革

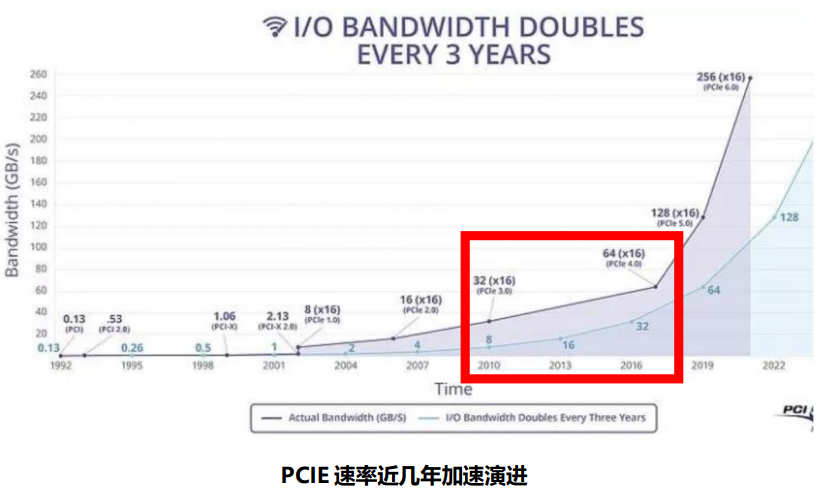

说到计算节点内数据传输接口,就不得不提PCIe,自从PCI-SIG组织在2003年推出了PCI-Express之后,计算机内部高速总线迎来了串行时代,当计算需求越来越高时,以太网开始回到摩尔定律的2年带宽改进周期,但是PCIe却没有跟上,成为瓶颈。PCIe 4.0 虽然姗姗来迟,但也满足了燃眉之急,使得GPU,FPGA等加速器和host之间的交互瓶颈得到缓解。近年来PCIe演进正在加速,以满足对日益增长的带宽需求。目前PCIe 5.0也已经商用,未来PCIe 6.0的协议也已经基本完成,单个PCIe 6.0 x16就可以支持800G以太网络。

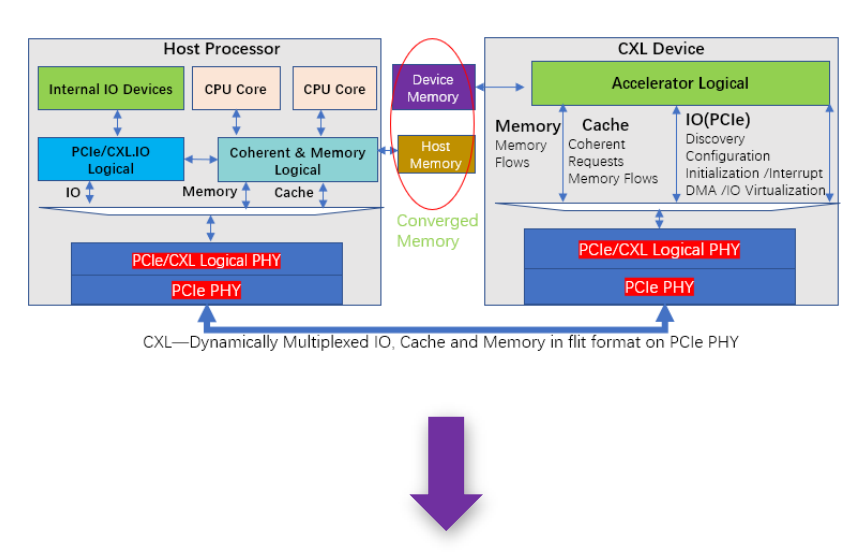

由于PCIe本身有很多问题,限制了目前计算架构的突破(例如树形结构,不支持一致性等),因此业界曾经产生了不少新的协议,例如开始由Xilinx主推后来由Arm商用的CCIX, IBM自己搞的OpenCAPI, AMD的Infinity Fabric以及NVidia的NVLink,以及多年前提出来的Gen-Z协议,到现在Intel最新的CXL。

目前看起来由于Intel在服务器市场强大的市占率和话语权,CXL的前景还是被普遍看好。其底层是沿用PCIe PHY(目前是5.0),上层协议进行了重新的建构。

除了我们熟悉的针对PCIE的局限性做出的新的设计,CXL也带了很多新的应用,内存是最典型的,它可以将内存和处理器解耦,串行化,并且CXL2.0的switch的支持,可以做到内存池化。这会大大提高访存效率,极大降低成本,增加灵活性。对服务器和数据中心的新计算架构带来更多可能性。CXL的推广将会持续推动PCIe快速成长。

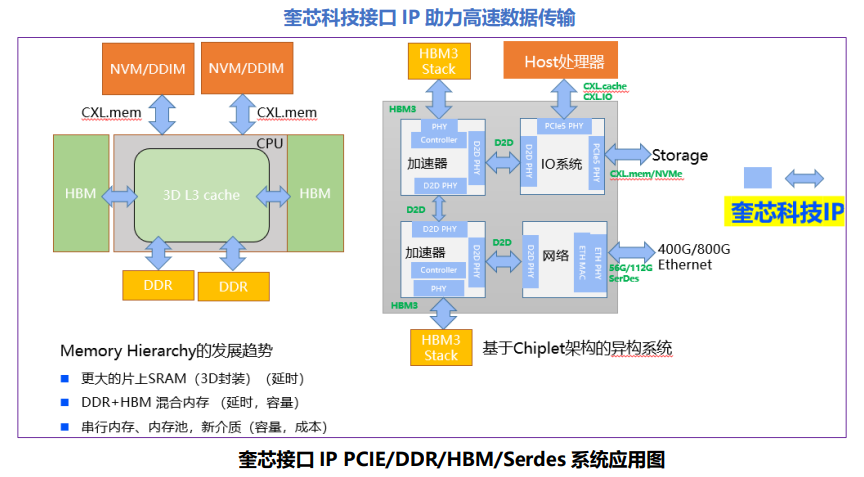

奎芯科技接口IP助力高速数据传输

奎芯接口IP PCIE/DDR/HBM/Serdes系统应用图

在未来的计算架构将从处理器为中心逐渐转变成以数据为中心同时,奎芯科技携手优秀研发团队已完成PCIe3/4的芯片认证(Silicon-Proven),被广泛应用于各类设备的数据传输,PCIe5正处于研发阶段。同时用于Chiplet高速互联的D2D/Serdes接口以及高带宽DDR5/HBM3也在同步开发中,预计2022~2023年将陆续推向市场,阻力高速数据传输。奎芯科技通过一系列的技术创新及优化升级,打破能效墙、优化墙、内存墙和高速IO墙,进一步释放计算潜能,秉持国产化IP的专业研发技术,结合半导体行业发展趋势,提供优秀的解决方案助力芯片设计企业!

关于奎芯科技(MSQUARE):

奎芯科技(M SQUARE)于2021年在上海注册成立,是一家专业的集成电路IP供应商。作为芯片产业链上游关键技术环节的企业,公司推出的高速接口IP,涵盖USB、PCIe、SATA、SerDes、MIPI、DDR、HDMI、DP、HBM等产品,聚焦高性能计算、人工智能、消费类电子、汽车电子、物联网等领域,致力于通过先进半导体IP研发与定制服务,打造市场急需的IP组合,积极响应中国快速发展的芯片和应用需求﹐全面赋能芯片设计产业。

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 2 研发收关:进迭时空高性能处理器核X100产品发布会震撼来袭

- 3 MediaTek天玑汽车平台推动汽车产业加速迈入AI时代,3nm旗舰座舱平台亮相

- 4 国内首颗,精准纠错!德明利TWSC2985系列:支持4K LDPC技术的存储芯片