美国大学推出新型晶体管,延续摩尔定律

来源:内容来自半导体行业观察(ID:icbank) 编译自allabourcircuit ,谢谢。

透明导电氧化物呈上升趋势

为了探讨这个问题,讨论为

什么氧化铟是普渡大学研究人员成功的关键因素可能是有用的。

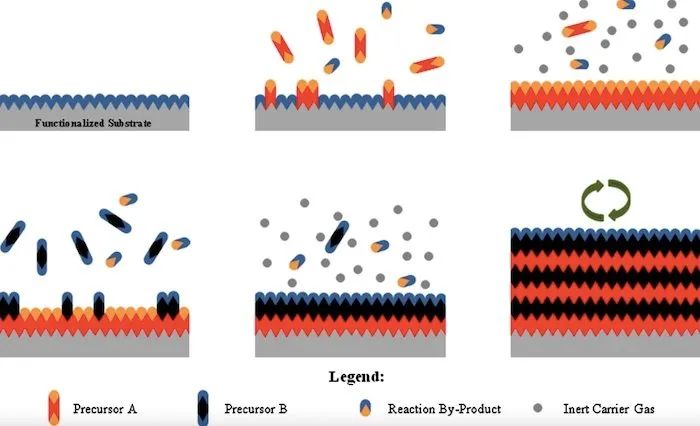

原子层沉积

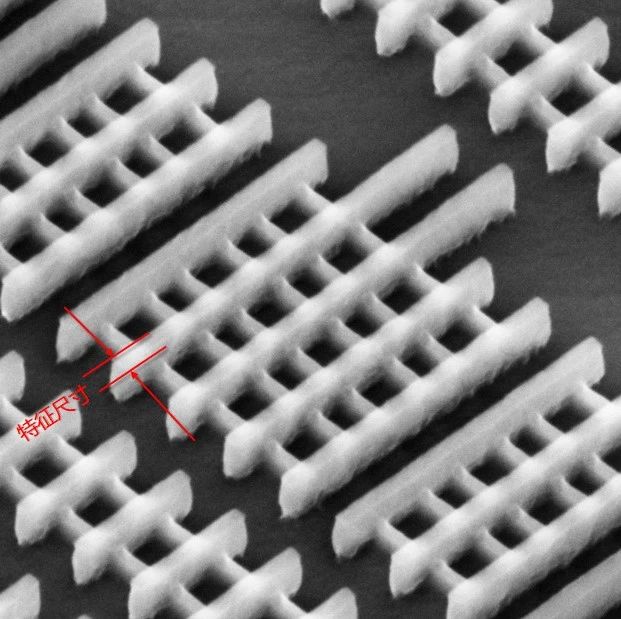

普渡大学研究人员通过

缩小晶体管推进半导体设计

-

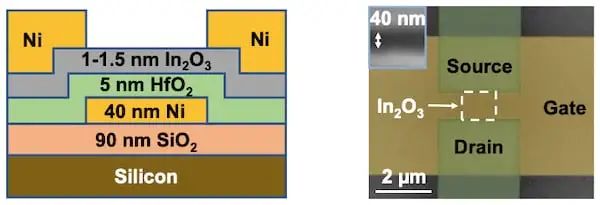

栅极金属:40nm镍

-

栅介质:5nm氧化铪

-

半导体通道:1/1.2/1.5nm氧化铟

-

源极和漏极触点:80nm 镍

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2968内容,欢迎关注。

推荐阅读

★ 3nm争夺战打响

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻