印度启动RISC-V处理器计划

来源:内容由半导体行业观察(ID:icbank) 编译自businesstoday ,谢谢。

印度发力RISC-V 处理器

-

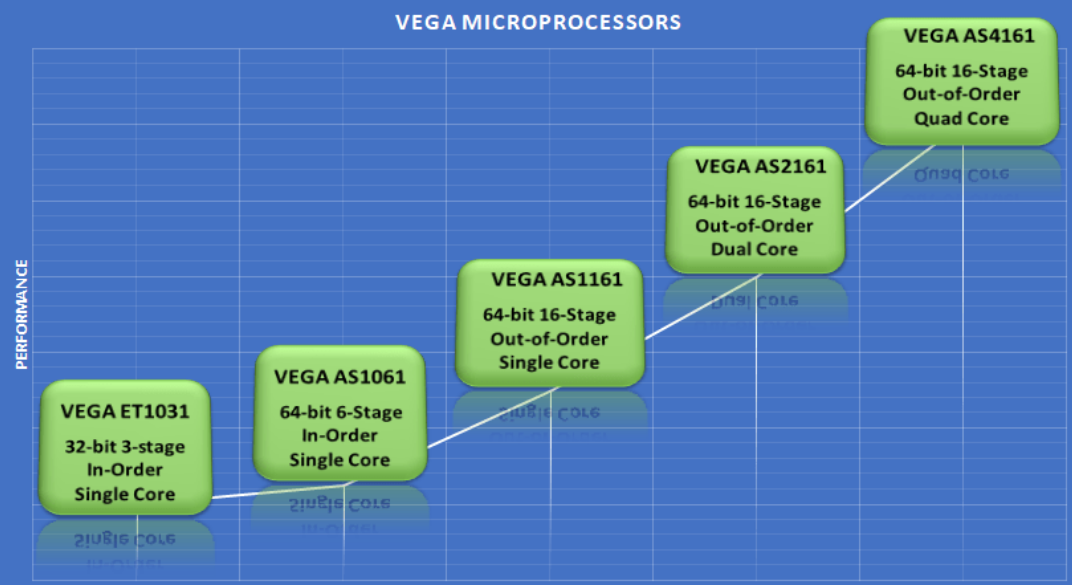

VEGA ET1031 – 32 位单核 3 级有序 RV32IM 处理器,带AHB/AXI4.bus,可选 MMU,可选调试 -

VEGA AS1061 – 64 位单核 6 级有序 RV64IMAFDC 处理器,具有 8KB D-cache、8KB I-cache、FPU、AHB/AXI4总线 -

VEGA AS1161 – 64 位单核 16 级流水线乱序 RV64IMAFDC 处理器,具有 32KB D-cache、32KB I-cache、FPU、AHB/AXI4/ACE总线 -

VEGA AS2161 – 64 位双核 16 级流水线乱序 RV64IMAFDC 处理器,具有 32KB D-cache、32KB I-cache、512KB L2 cache、FPU、AHB/AXI4/ACE 总线 -

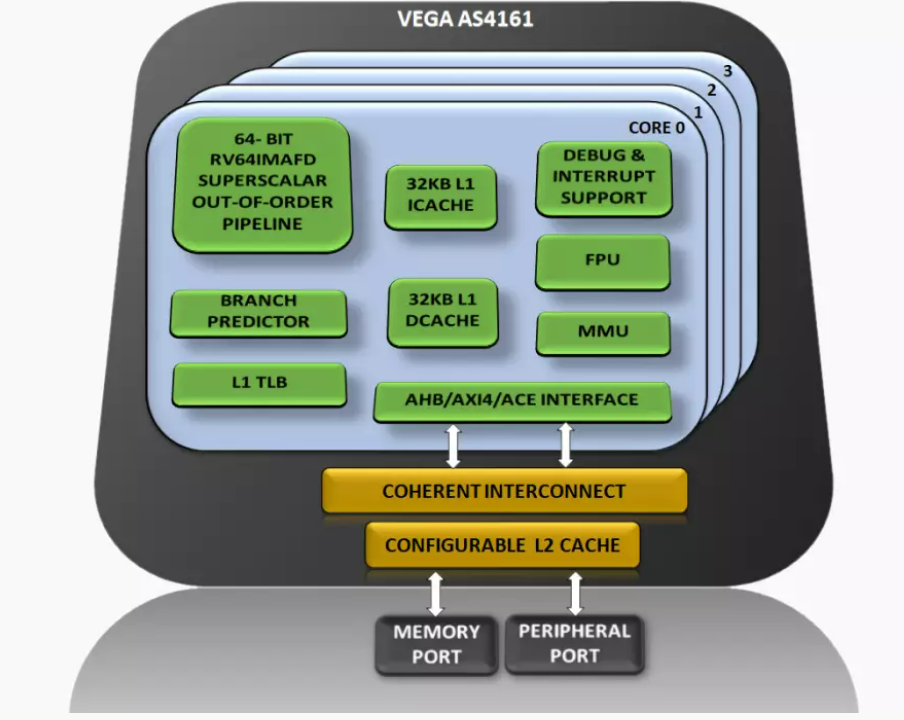

VEGA AS4161 – 64 位四核 16 级流水线乱序 RV64IMAFDC 处理器,具有 32KB D-cache、32KB I-cache、1024KB L2 高速缓存、FPU、AHB/AXI4/ACE 总线

-

RISC-V 64G (RV64IMAFD) 指令集架构

-

13-16阶段乱序流水线实现

-

高级分支预测器:BTB、BHT、RAS

-

哈佛架构,独立的指令和数据存储器

-

用户、主管和机器模式权限级别

-

支持 Linux 的全功能内存子系统

▪ 基于页面的虚拟内存

▪ 可配置的 L1 缓存

▪ 可配置的二级缓存

-

高性能多核互连

-

符合 IEEE 754-2008 的高性能浮点单元

-

AXI4- / ACE,兼容外部接口

-

平台级中断控制器

-

向量中断支持

-

高级集成调试控制器

-

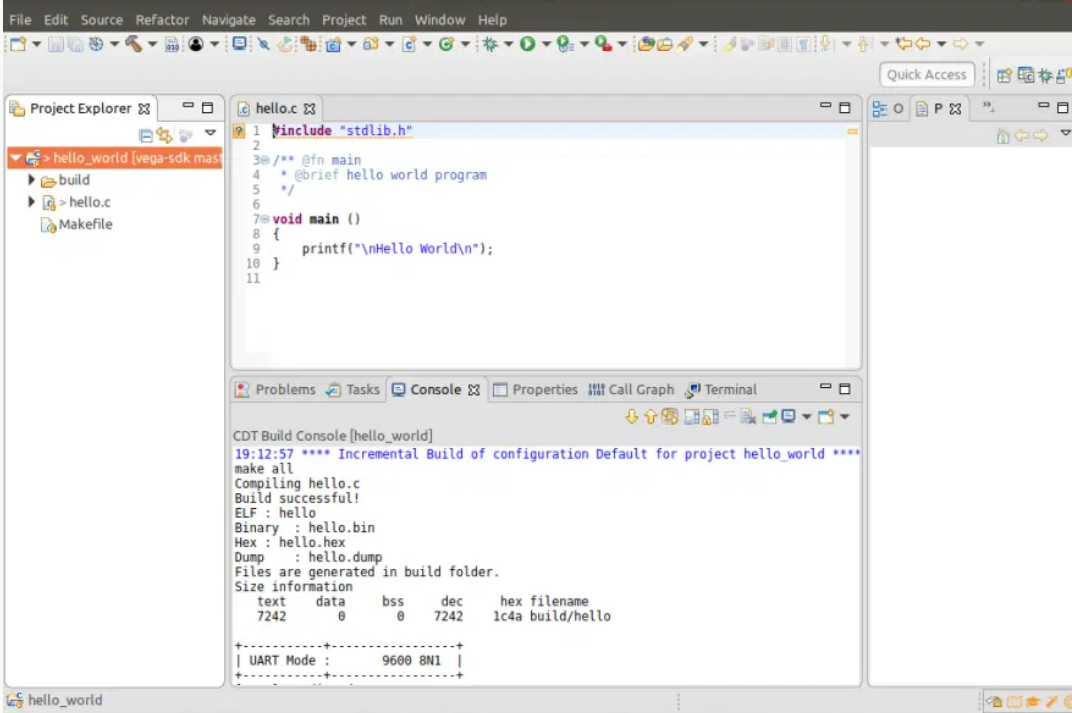

调试扩展允许通过 GDB >>openOCD >> JTAG 连接进行 Eclipse 调试

-

兼容 Linux

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3024内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 2 研发收关:进迭时空高性能处理器核X100产品发布会震撼来袭

- 3 MediaTek天玑汽车平台推动汽车产业加速迈入AI时代,3nm旗舰座舱平台亮相

- 4 国内首颗,精准纠错!德明利TWSC2985系列:支持4K LDPC技术的存储芯片