华为3D DRAM技术将亮相顶会

来源:内容由半导体行业观察(ID:icbank)综合 , 谢谢。

华为3D DRAM技术将亮相顶会

3D 堆叠开启DRAM新未来

DRAM作为一种易失性的、基于电容的、破坏性读取形式的存储器,在读取的时候会消耗电容器的电量,因此读取就要将该位写回到内存中。即使不进行读取,电荷最终也会通过晶体管从电容器中泄漏出来,从而随着时间的流逝而失去其明确定义的充电状态。虽然定期刷新可以保持数据,但这也意味着需要读取存储器的内容并将其重新写回。

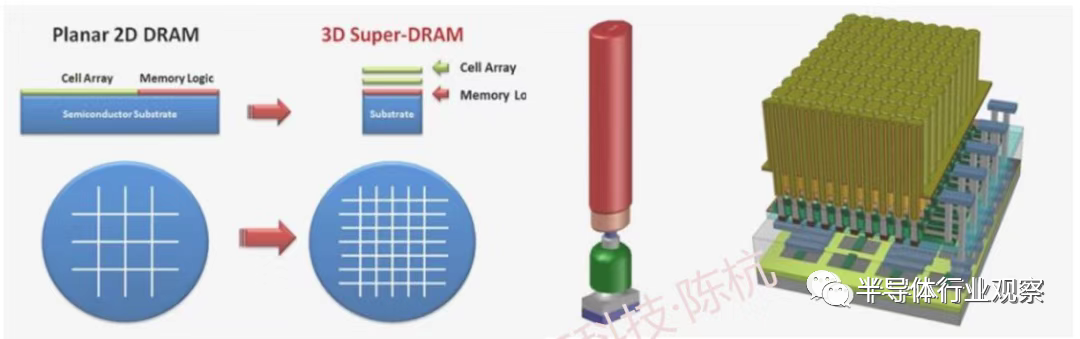

为了让DRAM更好地满足未来市场需求,业界也在不断地寻找新技术来突破目前的瓶颈,3D DRAM正是其中一个主流的技术方向。

图片来源:方正证券

图片来源:方正证券

除了片晶圆的裸晶产出量增加外,使用3D堆栈技术也能因为可重复使用储存电容而有效降低 DRAM的单位成本。因此,可以认为DRAM从2D架构转向3D架构是未来的主要趋势之一。

无电容IGZO,实现3D DRAM的候选者

HBM(High Bandwidth Memory,高带宽存储器)技术可以说是DRAM从传统2D向立体3D发展的主要代表产品,开启了DRAM 3D化道路。它主要是通过硅通孔(Through Silicon Via, 简称“TSV”)技术进行芯片堆叠,以增加吞吐量并克服单一封装内带宽的限制,将数个DRAM裸片垂直堆叠,裸片之间用TVS技术连接。从技术角度看,HBM充分利用空间、缩小面积,正契合半导体行业小型化、集成化的发展趋势,并且突破了内存容量与带宽瓶颈,被视为新一代DRAM解决方案。

除了HBM外,研究者们也开始在无电容技术方面下功夫,试图借此解决目前的难题。其实关于无电容,早有Dynamic Flash Memory、VLT技术、Z-RAM等技术出现,但日前,美国和比利时的独立研究小组IMEC在2021 IEDM 上展示了一款全新的无电容器 DRAM,这种新型的DRAM基于 IGZO(indium-gallium-zinc-oxide)可以完全兼容 300mm BEOL (back-end-of-line),并具有>10 3 s保留和无限 (>10 11 ) 耐久性。

据介绍,这些结果是研究人员在为单个 IGZO 晶体管选择最佳集成方案后获得的,而这个最佳集成方案就是具有掩埋氧隧道和自对准接触的后栅极集成方案。使用这种架构后,IGZO TFT(thin-film transistors)的栅极长度可以缩小到前所未有的 14nm,同时仍然保持大于100s的保留。通过EOT(equivalent oxide thickness)缩放控制阈值电压 (V t )、改善接触电阻和减小IGZO层厚度,可以进一步优化小栅极长度下的保持率。当后者的厚度减小到 5nm 时,甚至可以省略O 2 中的氧隧道和退火步骤,从而大大简化了集成方法。

(a) 示意图和 (B) 具有氧隧道和 14nm 栅极长度的后栅极架构中单个 IGZO 晶体管的 TEM 图像

(a) 示意图和 (B) 具有氧隧道和 14nm 栅极长度的后栅极架构中单个 IGZO 晶体管的 TEM 图像

总的来说,今年新推出的新型DRAM 通过对基于 IGZO 的 DRAM架构和集成的改进,使2T0C DRAM 存储器具有>10 3 保留、无限耐久性和栅极长度缩小至 14nm。更重要的是,这些突破性的成果都使得无电容IGZO-DRAM 成为实现高密度 3D DRAM 存储器的合适候选者。

但可以肯定的是,随着这些突破性技术的发展,DRAM 远未走到生命尽头,未来或将继续称霸存储器市场。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3048内容,欢迎关注。

推荐阅读

★ 芯片制造工艺可到0.2nm?

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 芯片验证挑战日益突出,西门子EDA携全新Veloce CS系统迎战!

- 2 研发收关:进迭时空高性能处理器核X100产品发布会震撼来袭

- 3 恩智浦发力边缘AI,为产业生态注入创新动能

- 4 澜起科技率先试产DDR5时钟驱动器(CKD)芯片