芯片的3D堆叠,IBM和东京电子公布新方法

来源:内容来 自interestingengineering , 谢谢 。

IBM Research 和 Tokyo Electron (TEL) 合作实现了 3D 芯片制造的新突破,该突破使用一种新颖的方法来保持摩尔定律的运行。

一份新闻声明显示,两家公司合作开展了一项芯片制造创新,该创新简化了使用 3D 芯片堆叠技术生产晶圆的过程。

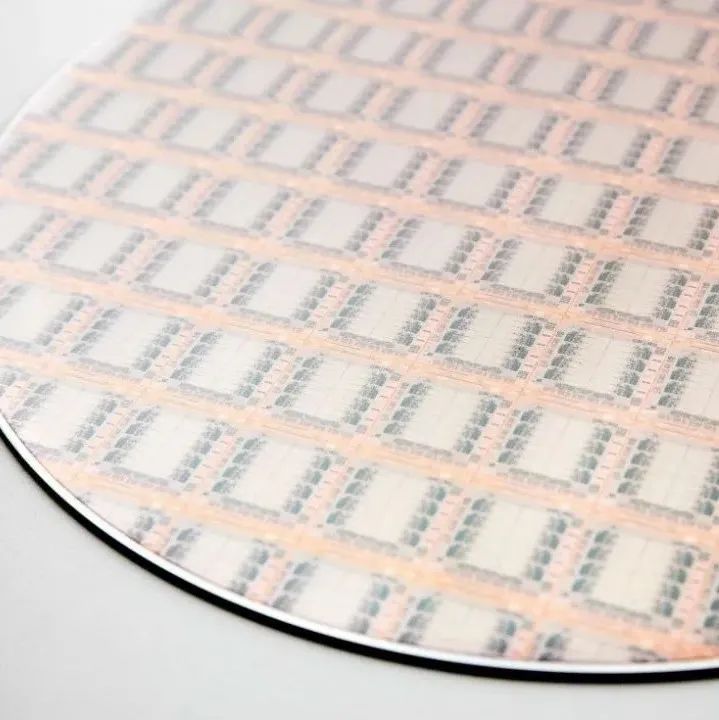

他们宣布,他们成功实施了用于生产 3D 芯片堆叠技术的 300 毫米硅芯片晶圆的新工艺。这是世界上第一个采用该技术的 300 毫米级示例。

新的芯片堆叠工艺使用硅不可见的激光

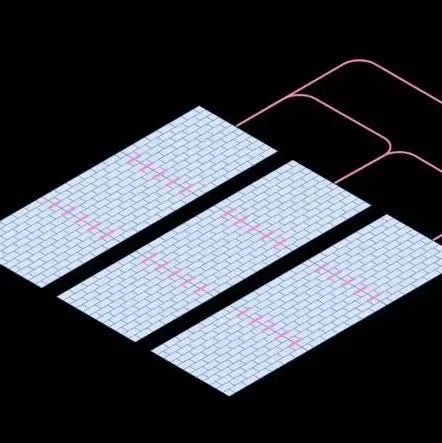

芯片堆叠通常需要硅层之间的垂直连接,称为硅通孔 (TSV)。这些层通常非常薄,厚度小于 100 微米。

在生产过程中,这些芯片中的每一个都连接到载体硅片上,该载体硅片通常由玻璃制成,临时粘合到硅上。处理完晶圆后,使用紫外激光将玻璃载体从硅中移除。

IBM 和 TEL 的新工艺使用一个 300 毫米的模块和一个红外激光来执行剥离工艺。这个过程对硅是透明的,这意味着它允许使用标准硅片而不是玻璃硅片作为载体。这意味着晶片可以粘合到其他硅片上,这意味着制造过程中不再需要玻璃载体。

IBM和TEL旨在缓解全球芯片短缺

新方法背后的研究人员认为,它可以帮助缓解全球芯片行业的压力。“随着全球芯片短缺的持续,”IBM 的声明中写道,“我们可能需要新的方法来增加未来几年的芯片产能。我们希望我们的工作将有助于减少半导体供应链中所需的产品数量,同时还有助于推动未来几年的处理能力改进。”

IBM Research 自 2018 年以来一直与 TEL 合作开发这一新工艺,该公司表示,在制造过程中与不同晶圆对相关的缺陷和工艺问题也应该会减少。接下来,合作伙伴的目标是进一步测试他们的 beta 系统,以展示如何在供应链中实施它。

全球芯片短缺是由于需求旺盛和 Covid 造成的工厂中断造成的。但即使在大流行之前,计算机芯片行业就已经感受到了压力。摩尔定律指出,微芯片上的晶体管数量每年将翻一番,但由于硅的物理限制而放慢了速度。专家说 ,晶体管正在接近它在保持功能的同时尽可能小的程度,导致一些人为摩尔定律敲响了丧钟。作为参考,IBM Research 的最小芯片节点为 2 纳米宽。

芯片堆叠通常仅用于高端操作,例如高带宽存储器的生产。但是,它有可能扩大特定体积中的晶体管数量。摩尔定律传统上侧重于面积而不是体积,这意味着新的突破允许通过对 1965 年著名观察的不同解释来延续摩尔定律。它可能还没有死。

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3094内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!