未来的处理器,长啥样?

来源:内容 由 半导体行 业观察(ID:icbank)编译自SE, 谢谢 。

近日,AMD 的首席技术官 Mark Papermaster 与半导体工程公司坐下来讨论了随着规模缩小带来的好处所需的架构变化,包括小芯片、异构集成的新标准和不同类型的内存。以下是那次谈话的摘录。

首先,在闻到五年后处理器会是什么样子的时候?Mark Papermaster回应说,毫无疑问,处理的未来是异构的。

在他看来,未来的处理器将会是多个计算引擎协同工作,因为海量数据和到处都需要图形处理。数据中心和个人电脑都需要它,而物联网数据的爆炸式增长需要对整个产业链进行分析和可视化,这显然需要特定领域架构的芯片。根据Mark Papermaster的分享,CPU 非常适合一般处理,并且有大量的应用程序可以在 x86 和 Arm 上运行。对于更专业的图形和矢量处理,FPGA 或 ASIC 可以提供非常专业的计算。

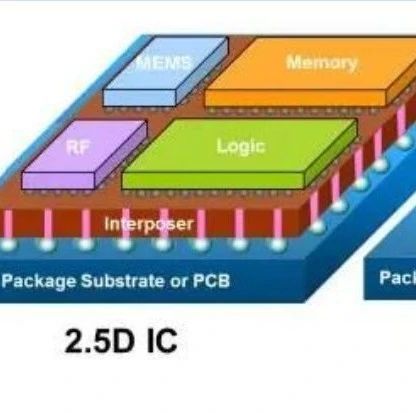

在讲到单凭节点升级,无法满足性能增长需求的时候,Mark Papermaster指出,这就意味着您必须针对该解决方案进行架构设计。一个很好的例子是 V-Cache,我们介绍的垂直缓存,在 CPU 芯片顶部有一个缓存,具有混合绑定。它只是一个纯金属连接,如果您正在查看一个缓存绑定应用程序,这将是一个巨大的优势,就像 EDA 使用的许多分析一样。

在验证您的 RTL 设计时,我们看到当您运行该应用程序时,您会获得显着的飞跃。因此,您必须构建解决方案。你必须知道你正在解决什么问题。然后,当你这样做时,你知道你所拥有的技术会真正带来价值,那么你真的必须考虑所有其他动人的部分。这将带来哪些挑战?我是否需要新的 EDA 功能对其进行建模?我需要新的模拟功能吗?我们需要解决哪些机械或热问题?您必须在设计过程中进行备份以构建测试芯片,并在您敢于推出第一款产品之前分析所有这些。你不能只希望它会奏效。你必须知道它会起作用。在将解决方案推向市场之前,确实需要经过多年的深思熟虑制定计划和战略。

关于chiplet商用和自用的问题。Mark Papermaster给出的答案是。

现在,大家都是内部开发chiplet,像这样的新创新也总是这样开始的,因为标准需要时间。我们在 Infinity 架构上进行了投资,这使我们能够连接我们的 CPU 或 GPU,现在通过收购 Xilinx 连接 FPGA。

谈到如何才能从自用走向商的时候,Mark Papermaste表示,首先,您需要一种方法将这些不同的 IP 组合在一起,以便它们和谐地工作。随着时间的推移,这可以扩展到一个生态系统系统,但它需要标准。如果你看看我们过去几年所做的事情,我们作为一个行业在标准方面取得了长足的进步,这些标准确实将支持chiplet行业。我们从一个有效的协议开始。在其初始实施中,它建立在 PCIe 的物理连接之上。但 CXL 协议确实将启用具有加速器和扩展内存选项的解决方案生态系统。想象一下,它进入了一个小芯片生态系统。这就是 UCIe 联盟的意图。

在问到封装将如何影响产业的时候。

Mark Papermaste告诉记者,有多种封装方法,因为需要解决不同的问题。每一个都是针对经济和物理限制而量身定制的,例如 I/O 连接的数量。但随着时间的推移会有一些整合。我们开始看到成本下降,因为其中一些封装方法达到更高的产量,这使得它们在经济上是可行的。然后你可以以此为基础。

晶圆级扇出就是一个很好的例子。随着它在一些消费产品中的大量使用,我们可以添加额外的连接层并在此基础上进行构建。我们可以在复杂性链中提高它并解决更多问题,同时利用晶圆级扇出方法的衍生产品。但这不仅仅是一个一揽子解决方案。对elevated fan-out bridges 以及混合键合的持续需求。这些元素中的每一个都将持续到未来,并且会有更多的创新。

这将是一个动态的空间,我们可以在其中进行调整,并且可以在给定的技术方法背后获得数量以降低成本。当你降低成本时,你就会引入越来越多的产品可以利用这种方法,它就变成了一种大众市场的解决方案。

在问到关于摩尔定律未来,以及是否会有2nm chiplet的时候。Mark Papermaste表示,的确,摩尔定律的继续确实越来越难了。这意味着您创建那些性能最高的设备的成本确实在上升。

二展望未来,您必须更加谨慎地选择在何处应用新技术。过去,我们同时需要 PPA——功率、性能和面积优势,并在每个新节点上降低成本。现在,我们必须更有选择性。您可能无法获得与以往一样多的功率优势或晶体管的最大频率优势。但是您必须查看整个方程式以及您的产品在哪里获得显着的经济利益。即使成本更高,您仍然希望获得这些好处,因此您希望对其进行架构,以便您使用的电路从新技术中获得最大收益。

我们将需要更多的异构设计和更多的chiplet。

Mark Papermaste同时谈到,他们与业内合作伙伴一起对存储进行创新,而且整个项目进展顺利,除此之外。也有正在评估的新内存结构。他们需要时间。您可以很快地进行架构更改,但是当您拥有用于高级记忆的新材料时,这需要几年时间。这是一个创新的成熟领域,因为我们需要的所有这些需要大量计算的应用程序都同样需要内存。并且该内存需要以较低的功率工作,并且需要处于它们所支持的计算元素可以接受的延迟。

“对于新的存储设备结构,有几种创新方法,它们要么是独立的,要么是对任何给定单片芯片中的工艺进行更改。在内存处理方面有很多非常好的工作正在进行。”Mark Papermaste说。

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3102内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 芯片验证挑战日益突出,西门子EDA携全新Veloce CS系统迎战!

- 2 研发收关:进迭时空高性能处理器核X100产品发布会震撼来袭

- 3 固本培元,Qorvo拓展多元化业务版图

- 4 中国移动发布了一颗芯片:本土首颗400Gbps DPU