[原创] 台积电披露未来的研发计划

据semiwiki报道,在最近的VLSI技术与电路研讨会上,台积电研发高级副总裁YJ Mii博士发表了题为“Semiconductor Innovations, from Device to System”的演讲。该演示文稿提供了对台积电未来研发计划的见解,超越了当前的路线图。还强调了正在研究的技术的相关挑战。本文总结了 Mii 博士的精彩演讲。

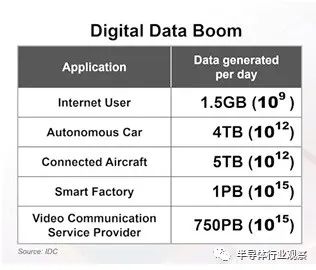

Mii 博士首先对未来终端市场的增长进行了预测,并强调了持续提高高性能计算吞吐量的必要性和对能效的关注。对于 HPC 的需求,他分享了一个“数字数据热潮”的预测,如下图所示。例如,“智能”工厂预计每天收集、监控和分析 1 PB 的数据。

他进一步指出,机器学习(训练和推理)对上述应用的支持的作用同样预计也会扩大,这对 HPC 吞吐量提出了进一步的要求。Mii 博士评论说,这些 HPC 要求将继续推动研发工作,以提高半导体工艺路线图和先进(异构)封装技术中的逻辑密度。

下图则展示了台积电对电源效率的不懈关注。

所示架构不仅说明了 5G(很快,6G)将在我们使用的设备中普及的程度,而且还说明了“边缘数据中心”的运营。与 HPC 应用程序一样,机器学习算法的影响将无处不在,需要关注功率效率。

最近的技术创新

在介绍台积电的一些研发项目之前,Mii 博士简要总结了最近的半导体工艺技术创新。

在节点 N7+ 引入 EUV 光刻

台积电表示,台积电的 N7+ 技术于 2019 年第二季度开始量产,是首个将客户产品大批量投放市场的 EUV 工艺。采用 EUV 技术的 N7+ 工艺建立在台积电成功的 7nm 节点之上,为 6nm 和更先进的技术铺平了道路。其中,台积电 Fab 15 是N7+ EUV 的生产基地。

他们进一步指出,N7+ 量产是 Fab 15 中有史以来最快的量产之一。它的产量与已经量产一年多的原始 N7 工艺相似。在N7+ 引入EUV的时候,台积电的 EUV 工具已达到生产成熟度,工具可用性达到了大批量生产的目标目标,日常操作的输出功率超过 250 瓦。

据台积电在早前的技术大会上介绍,统计全球已经安装的EUV光刻机系统中,他们拥有了其中的 55%。他们进一步指出,公司将在 2024 年拥有ASML下一个版本的最先进芯片制造工具——high-NA EUV。

据anandtech报道,如今,最先进的芯片采用 5/4 纳米级工艺制造,使用 EUV 光刻 ASML 的 Twinscan NXE:3400C(和类似)系统,该设备具有 0.33的 数值孔径 (NA) 光学器件,可提供 13 nm 分辨率。该分辨率对于 7 nm/6 nm 节点(间距为 36 nm ~ 38 nm)和 5nm 节点(间距为 30 nm ~ 32 nm)的单模式方法来说已经足够好了。但随着间距低于 30 nm(超过 5 nm 节点),13 nm 分辨率可能需要双光刻曝光,这将在未来几年内使用。

因此对于后 3nm 节点,ASML 及其合作伙伴正在开发一种全新的 EUV 工具——Twinscan EXE:5000 系列——具有 0.55 NA(high-NA)镜头,能够实现 8nm 分辨率,预计可避免在 3 nm 及以上使用多重图案。新的high-NA扫描仪仍在开发中,预计它们将非常复杂、非常大且价格昂贵——每台的成本将超过 4 亿美元。高数值孔径不仅需要新的光学器件,还需要新的光源,甚至需要新的晶圆厂大楼来容纳更大的机器,这将需要大量投资。

“台积电将在 2024 年引入high-NA EUV 扫描仪,以开发客户所需的相关基础设施和图案化解决方案,以推动创新,”台积电研发高级副总裁 YJ Mii 在台积电硅谷技术研讨会上表示。Mii没有透露该设备何时用于大规模生产,该设备是用于制造更小更快芯片的第二代极紫外光刻工具。台积电的竞争对手英特尔公司表示,它将在 2025 年之前将这些机器投入生产,并且它将是第一个收到该机器的公司。

用于提高载流子迁移率的 SiGe pFET 沟道

按照台积电所说,在他们的7nm节点之前,硅一直是所有 CMOS 技术世代的首选晶体管沟道材料。但到了台积电的 5nm 技术,他们率先以 SiGe 作为 p 型 FinFET 沟道材料,以用于先进逻辑生产技术。台积电强调,公司还在积极探索替代晶体管沟道材料,为高性能和低功耗器件设计提供额外自由度。硅锗和锗是台积电探索性研究工作的例子,这些工作已被广泛发表,并在某些情况下被公认为国际会议的亮点。

从上图可以看到,高迁移率沟道晶体管改进了驱动电流(+18%)。一开始,有人评论说这可能是锗沟道(fin),但考虑到 Ge 和 Si 之间的晶格不匹配以及会产生的位错,我们似乎更有可能拥有类似的 PMOS SiGe 沟道,台积电上面的介绍说明了这点。与 IBM 联盟的平面栅极优先 HKMG 部件中使用的相比,含有高达 40% 的 Ge。

分析表示,在平面版本中,epi-SiGe 首先生长,然后在 NMOS 区域中去除,在这种情况下只有 3-5 nm。如果有源fin高度约为 55 nm,总fin高度约为 120 nm,这是一个不同的挑战,但考虑到台积电在纳米片器件上的所有工作,现在可以认为他们可以对 SiGe 与 Si 进行了非常选择性的蚀刻。不过,对台积电而言,后续更大的问题是,如果使用这种方法,SiGe fin将比Si fin高几十纳米,增加了后续加工的复杂性。

相关分析进一步指出,为了使fin保持在同一水平,我想我们可以对 N 或 P 区域进行蚀刻,然后进行 Si 或 SiGe 外延加 CMP(或选择性外延?),具体取决于蚀刻的区域;这似乎也不简单。而且我认为我们会对 Si 和 SiGe 鳍片进行单独的fin定义蚀刻,这听起来也很混乱——也许fin蚀刻现在也是 EUV实现?

设计技术协同优化 (DTCO)

Mii 博士强调了工艺技术开发如何演变为更加重视 DTCO,评估工艺复杂性和设计改进之间的权衡已成为工艺开发的一个组成部分。他强调了最近采用的有源栅极接触和单扩散中断工艺步骤作为示例。他补充说:“DTCO 的工作不仅限于逻辑设计——存储器和模拟电路也是 DTCO 评估的关键方面。”

台积电表示,设计技术协同优化诚如其字面所示就是设计与制程技术寻求整合式的优化,来改善效能、功耗效率、电晶体密度、以及成本,在支援新的制程技术时通常历经重大的架构创新,而非提供与前一代技术完全相同的结构,仅有做到更小而已。

他们指出,DTCO的果实绝非唾手可得,制程研发团队与设计研发团队一开始就必须携手合作,针对下一世代技术的定义进行设计技术协同优化,两个团队必须保持开放的心态,探索设计创新与制程能力的可能性,许多创新的想法都在这个阶段被提出来,其中有些想法可能太积极而无法借由既有技术实现,有些想法初步看起来可能很有潜力,但是结果却没那么实用,设计技术协同优化的目的就在于定义真正有意义的调整,超越单纯的几何微缩,进而达成提升效能、功耗、面积的目标。

完成设计技术协同优化的参数定义之后,下一步则是寻出“制程窗口”的极限,借由密集来回的互动过程调整,定义制程的范围边界以达成最佳的效能、功耗、面积,并仍可以高良率大量生产。

为了确保设计技术协同优化创新带来的效能、功耗、面积优势能够应用在客户的产品上,台积公司与开放创新平台联盟之电子设计自动化伙伴携手合作,使用的工具能够精准符合新的制程设计法则,充分利用新的技术优化来进行设计最佳化并达成效能、功耗、面积的目标。

关于台积电对DTCO的看法,参考文章 《台积电官方科普:什么是DTCO?》

2nm时候引入的纳米片

台积电的 N2 是一个全新的平台,广泛使用 EUV 光刻技术,并引入了 GAAFET(台积电称之为纳米片晶体管)以及背面供电。新的环栅晶体管结构具有广为人知的优势,例如大大降低了漏电流(现在栅极围绕沟道的所有四个边)以及调节沟道宽度以提高性能或降低功耗的能力. 至于背面电源轨,它通常旨在为晶体管提供更好的电力输送,为后端 (BEOL) 中电阻增加的问题提供解决方案。新的电源传输旨方案在提高晶体管性能并降低功耗

从功能集的角度来看,台积电的 N2 看起来是一项非常有前途的技术。至于实际数字,台积电承诺 N2 将让芯片设计人员在相同功率和晶体管数量下将性能提升 10% 至 15%,或者在相同频率和复杂度下将功耗降低 25% 至 30%,同时,与N3E 节点相比,芯片密度增加了 1.1 倍以上。

与 N3E 相比,台积电 N2 节点带来的性能提升和功耗降低与代工厂的新节点通常带来的效果一致。但所谓的芯片密度提升(应该反映晶体管密度增益)仅略高于 10% ,这并不是特别鼓舞人心,特别是考虑到与普通 N3 相比,N3E 已经提供了略低的晶体管密度。

未来半导体技术创新

在演讲中,Mii博士随后介绍了针对未来应用需求的几项半导体技术研发工作。

他首先谈到的就是CFET (complementary FET)。

经过几十年的平面 FET 器件技术,FinFET 也经历了相当长的寿命,从 N16/N12 到 N7/N6 到 N5/N4 到 N3/N3E。看看基于纳米片器件的工艺节点如何发展将会很有趣。从Mii 博士的介绍我们可以看到,在纳米片之后,台积电专注于 CFET 器件的引入。

如下图所示,CFET 工艺保留了环栅纳米片的优点,但垂直制造了 pFET 和 nFET 器件。(图中pFET在底部,nFET在顶部。)

在上面描述的反相器逻辑门的横截面中,突出显示了两个器件的公共栅极输入和公共漏极节点。下图扩展了 CFET 器件堆叠所带来的工艺开发挑战,特别是对高纵横比蚀刻和相关金属沟槽填充的需求,以实现上面强调的垂直连接。

现在,研究 CFET 工艺开发的不同研究人员一直在追求两条路径:一种“顺序”(sequential)工艺,其中 pFET 和 nFET 器件使用用于顶部器件制造的上部减薄衬底实现,该衬底在底部器件制造后接合到起始衬底,中间有一个介电层;

一种“单片”(monolithic)工艺,其中有一组外延层用于衬底上的所有器件。在工艺复杂性和热预算、设备性能优化(在顺序流程中使用多种基板材料)以及两种方法之间的成本方面存在权衡。

虽然 Mii 博士没有具体说明,但有关high AR 蚀刻和金属填充的评论表明,台积电的研发重点是单片 CFET 工艺技术。

有关CFET的更多介绍,参考文章 《1nm后的晶体管,imec将CFET纳入路线图》

其次,二维晶体管材料是台积电关注的另一个方向。

有积极的研究评估用于场效应晶体管沟道的“后硅”材料。如下所示,随着器件栅极长度和沟道体厚度的减小,2D 材料提供了改善载流子迁移率和亚阈值斜率的潜力(具有更低的漏电流和更低的 VDD 操作的潜力)。

2D 工艺开发的主要挑战之一是为器件源极/漏极节点提供低接触电阻连接。Mii 博士分享了台积电研究人员先前发表的结果,重点介绍了对铋 (Bi) 和锑 (Sb) 的评估——与之前发表的工作相比,Rc 降低了 5 倍,如下所示。

在2021年,中国台湾大学、台积电与麻省理工学院(MIT)共同发表研究,首度提出利用「半金属铋」(Bi)作为二维材料的接触电极,可大幅降低电阻并提高电流,使其效能几与硅一致,有助实现未来半导体1纳米的挑战。

此次由台大、台积电与麻省理工学院(MIT)共同发表的研究,首先由美国麻省理工团队发现在二维材料上搭配半金属铋(Bi)的电极,能大幅降低电阻并提高传输电流。随后台积电技术研究部门(Corporate Research)将铋(Bi)沉积制程进行优化,台大团队并运用氦离子束微影系统(Helium-ion beam lithography)将元件通道成功缩小至纳米尺寸,终于获得这项突破性的研究成果。

台大电机系暨光电所吴志毅教授进一步说明,使用铋为接触电极的关键结构后,二维材料电晶体的效能不但与硅基半导体相当,又有潜力与目前主流的硅基制程技术相容,有助于未来突破摩尔定律的极限。虽然目前还处于研究阶段,但该成果能替下世代芯片提供省电、高速等绝佳条件,未来可望投入人工智能、电动车、疾病预测等新兴科技的应用。

第三,BEOL 互连架构。

后端互连的缩放面临着现有(镶嵌:damascene)铜线效率较低的挑战。镶嵌沟槽中的Cu扩散阻挡层(Cu diffusion barrier,例如,TaN)和粘附衬垫(adhesion liner,例如,Ta)占据了按比例缩放的导线横截面的增加百分比。Cu 沉积晶粒尺寸(deposition grain size )也受到限制,导致更大的电子散射(electron scattering)和更高的电阻率。下图突出了台积电为引入一种新的(subtractive-etched)BEOL 技术所做的研发工作。

通过subtractive metal 工艺,引入了制造导线之间电介质的新机会——上图说明了相邻电介质内的“air gap”横截面。

台积电卓越科技院士暨研发副总余振华在之前曾表示,台积的3D Fabric平台已建立且率先进入新阶段,已从异构整合、系统整合到现在的系统微缩,相关发展类似系统单芯片(SoC)的微缩,讲究效能耗能与尺寸微缩,系统微缩新阶段则是追求更高系统效能、更低耗能,以及更紧密尺寸变成体积上的精进。

余振华提到,异构整合技术在台积电从倡议到开花结果,已变成业界新显学,将能为半导体提供更多价值。相信不论前段制程或后段制程产业都乐见半导体的这样的发展。台积电也观察到,目前系统微缩类似SoC已从过去在效能、功耗及面积进一步升级,转为追求体积微缩。

不过,相关技术发展也有两大挑战,第一个是成本控制,在成本控制上,因为先进封装是微米等级,但目前制程早已进入纳米,制程整合若运用台积BEOL前段制程或传统封装设备切入都需要改善,比如铜制程设备成本就是一个挑战,控制不是问题,但导线宽度大小、时间消耗都较多是成本问题。

第二则是精准度,余振华说,借重BEOL前段制程来说,相关材料成本控制与效率是挑战,但若用传统后段的设备来做,则有精准度的挑战,这两种挑战都是希望产业上下游一起来努力,也由SEMI扮演中间者来共同推进。

有关BEOL,请参考文章 《1nm的关键技术,IMEC公布新进展》 。

最后,台积电谈到了二维导体(2D conductors)。

上图显示了二维导体层的横截面,以及与可比较的铜线厚度相比所产生的导电性优势。

Mii 博士没有详细说明正在评估的具体材料。例如,有许多过渡金属化合物在 2D 晶体拓扑中表现出高载流子迁移率,以及堆叠这些层的能力,这些层由van der Waals forces影响。

最后,Mii 博士以下图显示的幻灯片结束了他的演讲。他表示,未来的系统设计将利用以下技术:

-

增加晶体管密度,例如 CFET 器件(以及以 DTCO 为重点的工艺开发);

-

新型互连材料;

-

在先进封装中增加异构功能的集成,包括 2.5D 和 3D 配置中的chiplet和 HBM 堆栈;

-

用于系统设计分区、物理实现和电/热分析的新方法;

semiwiki表示,无论是对于设计师还是工艺技术工程师,现在进入这个行业都是一个激动人心的时刻。

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3106内容,欢迎关注。

推荐阅读

★ 中国大芯片浪潮

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻