关于台积电2nm,我们来谈谈

来源 :内容来自ctimes,谢谢。

在十年之前,谈2纳米(nm)制程芯片的量产,那简直就像天方夜谭,几乎是难以想像的生产技术。但如今,台积电已经正式宣布了量产时程,这个原本市场以为不可能的芯片制程技术,将会在2025年正式量产。

而台积2nm技术的宣布有什么重要性?它又会带出哪些半导体制造技术的风向球?本文就从技术演进,以及竞争与成本的角度来切入分析。

FinFET微缩之路划上休止符

台积电的2nm技术的宣布,单就技术上来说,就是正式宣告「鳍式场效晶体管(FinFET)」的微缩之路的终结。这个堪称是近十年以来,台积电最具竞争力的芯片制程技术,最终都须止步于3nm。

毫无疑问,FinFET是个好东西,它除了让摩尔定律得以延续外,同时也让晶圆制造厂可以持续提升芯片的效能并缩小体积。它最大的特色就是采用了立体式的结构,改善了MOSFET的电路控制性能,并减少漏电流的发生,另一方面也缩短了晶体管的闸长。

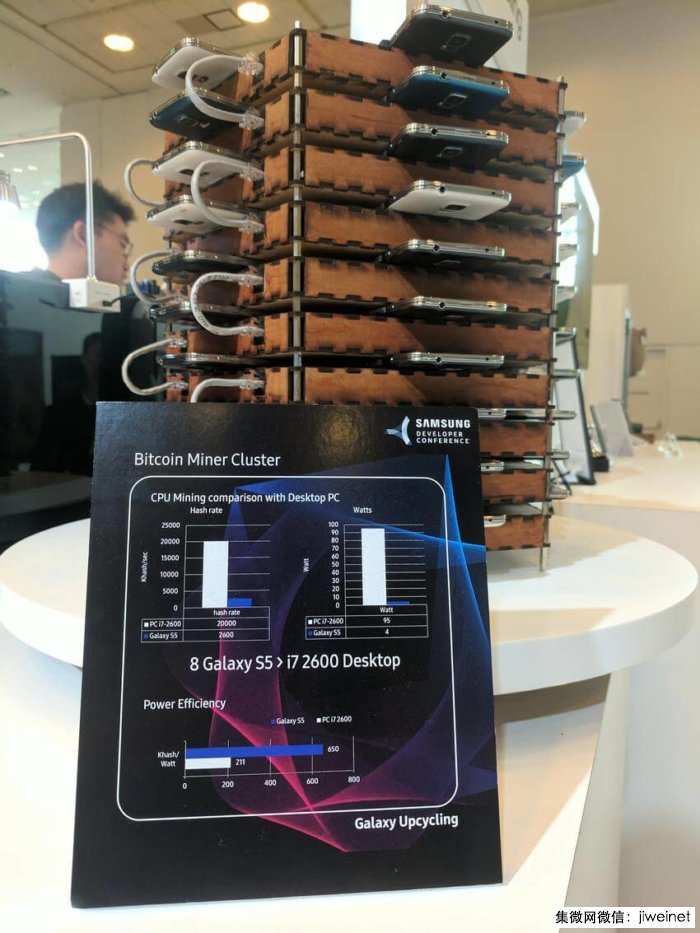

图一: 台积在2013年11月宣布成功试产FinFET,采用16nm生产制程。(source:TSMC)

台积是在2013年11月宣布成功试产FinFET,而当时所采用的生产制程是16nm;英特尔则是更早于台积,是在2011年就已经推出了商业化的22纳米FinFET制程技术。

至于三星,则是在14nm制程才采用了FinFET架构,不过当时他们是处于追赶的位置,还因此跳过了20nm制程,直接进攻一个全新世代的技术,并且取得了相当的成果,可以说是一次成功的策略。

但走到现在,也就是4nm和3nm这个关口,FinFET的微缩之路终究来到了尽头。由于单片的鳍式晶体管结构在这个制程之下,其电子控制的效能会大幅度的衰减,变得十分不稳定,因此难以作为先进运算的核心技术,自然也无法延续摩尔定律对性能提升的要求,于是采用新架构的呼声就不断在产业界与学研界里响起。

虽然FinFET制程到了5nm以下就变成了一个关卡,但台积依然透过他们强大的芯片制造能力,硬是让FinFET走到了3nm。而三星则是选择在此节点转向次世代制程。这除了显示台积超越业界的制造能力外,更凸显了台积对于获利与成本控制的高度重视。

三星抢推GAAFET制程企图弯道超车

洞悉到FinFET的极限之后,晶圆制造业者们当然就开始着手进行相关的研究布局,以因应未来的先进制程服务之争。但说白了,现在市场上也就只剩下三星和台积两家公司有能力进行实际的量产,所以目前若要寻求3nm以下的芯片制造服务,就是一个非T及S的局。谁先端出,谁就赢了,至少表面上是这样子。

也由于现在这两强之争的局面,让落后的三星不得不采行较为激烈的「弯道超车」策略,企图在3nm这个制程世代上,就开始导入新的晶体管架构技术,并期望借此追上,甚至是超越台积电。

而三星他们选择的制程称为GAAFET「Gate-All-around Field-Effect Transistor」。

依据三星的说明,它们的GAAFET是一种采用自行研发通道较宽的纳米片结构,也就是自有的「MBCFET(Multi-Bridge Channel FET)」技术。相较于较窄的纳米线GAA技术架构,这种宽型的结构可以带来更高的效能与更佳的能源效率。

图二: 三星GAAFET制程技术的示意图。

(source:三星)

此外,三星也指出,相较于5nm制程,他们第一代3nm制程能降低45%功耗、提升23%效能、缩减16%面积;第二代3nm制程则可降低50%功耗、提升30%效能,并缩减35%面积,可全面优化芯片PPA指标。

但三星这个技术的宣布,最重要的还是宣传的目的,因为三星所有的盘算就是要抢先台积之前,让市场知道,他们的GAAFET已经开始正式量产,而且是全球第一家的3nm芯片制造商。

不过其实是不是3nm并不这么重要,最值得关心的,是三星开始导入了新的晶体管制程技术。但到目前为止,他们良率与客户都属于未知的状态,成本与获利更是仍待观察。

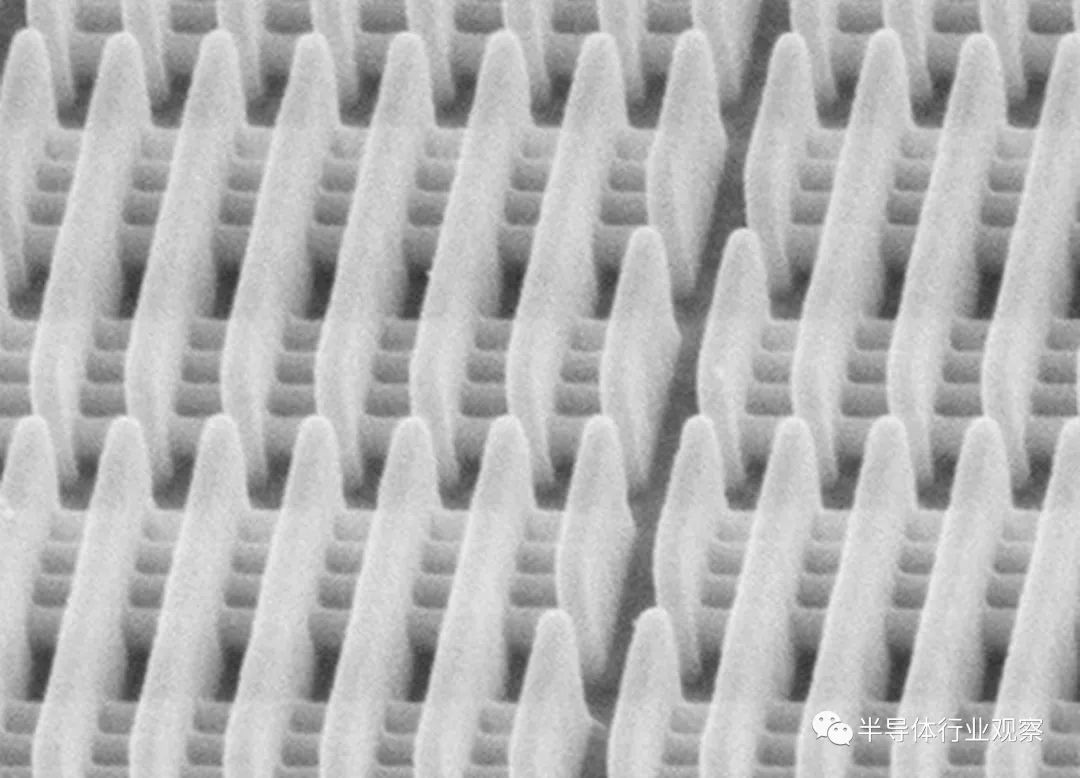

台积以王者之姿稳稳跨进纳米片世代

尽管三星没有特别强调,但我们从其所提供技术示意图来看,就可以得知他们的GAAFET技术就是一种纳米片(Nanosheet)架构,而这跟台积所发表的N2技术,其实都是属于同一种技术类型。换句话说,未来市场上2nm以下的制程芯片,都会是使用纳米片架构的晶体管。

相较于三星采用大动作追击的策略,台积对于导入纳米片架构制程就显得保守且小心,或者说是一种不疾不徐的态度。我们回顾台积选择进入FinFET制程的时间点来看,就可以端倪出这家公司的决策文化。

一来,他们已是市场的领先者,稳健拓展业务远比大胆推进技术更为重要;再者,台积一向看重生产良率和高获利率,不稳定、不够成熟的制程,他们定不敢,也不会贸然进行量产。

就因为这立场与策略的差异,因此台积选择进入纳米片架构的时间点,也就晚了三星一个世代。而这个一世代的差异,除了让台积在3nm制程上有更好的成本优势外,也为他们的2nm制程取得了更多的研发和试产的时间。

依据台积自己公布的资料,相对于N3,新一代的N2技术在相同功耗下,速度提升了10~15%;在相同速度下,则功耗降低25~30%。而在应用领域方面,N2将会推出针对行动运算的基本版本,另也会推出高效能版本和小芯片整合的解决方案,预计在2025年开始量产。

不过这里就有一点性能上的差异,因为三星的3nm GAAFET是对比5nm FineFET,而台积N2则是对比N3,所以单就各自帐面上的性能提升来看,纳米片架构的的确确是能够突破FinFET的极限。若是比较双方的数据差异,则台积拥有微缩制程上优势,其2nm具有较好的功耗表现。

不过三星的2nm制程也预计在2025量产,目前其实际的效能数据则仍未公布。

图三: 台积与三星的纳米片结构制程比较。

纳米片成为产业共识但谁会需要2nm技术?

对于台积与三星皆选择了纳米片架构作为下一代的制程技术,其实一点都不令人意外,甚至可以说是一种必然的结果。比利时微电子研究中心(imec)就曾在一篇技术文章中指出(注1),纳米片可以视为FinFET的自然演变,它能让许多针对FinFET制程应化的模组,都能沿用至纳米片制程。也促使业界更容易接受这套新架构。

不过,FinFET与纳米片毕竟不相同,在制程上仍有不小的差异。Imec也指出了它们的四大关键差异,且需要特别研发创新技术。

首先,纳米片会利用矽(Si)与矽锗(SiGe)进行多层的磊晶成长,致使传统的CMOS制程不再适用。而且整个堆叠会进行图形化,制成高深宽比的鳍片,因此确保纳米片的型态是个挑战。

第二个差异,是需要导入一层内衬层,也就是增加一层介电层来隔离闸极与源/汲极,进而降低电容。

第三个差异是纳米片制程多了一个释出通道的步骤,而此过程需要高度选择性,才能把少量的锗留在纳米片之间,并降低矽材的表面粗糙度。

第四个差异是替代金属闸极的整合,包含在纳米片周围与彼此间的间隙内沉积金属,并进行图形化。

而从imec所指出的制程挑战可以看出,进入纳米片结构制程的困难其实不小,直接造成的就是制造成本将大增,同时短时间内的良率应该不会太高,真要下单投入生产,所要承担的商业风险其实不小。尤其是目前3nm制程的生产成本已经将近6亿美元,若再往下走到纳米片的2nm,则金额实在难以想像。

所以综合来看,届时能有足够资本实力可以下单2nm制程芯片的业者,其实已经屈指可数。目前看来如果不是苹果(Apple),就是全力追求高性能与低高耗的绘图与处理器业者,例如NVIDIA和AMD,其他的行动运算平台业者如高通或联发科等,现在都还难以推估他们届时是否具备足够的商业能力来投单。

当然,Google和Amazon,或者特斯拉,也有可能投单2nm芯片,因为他们的资本更加庞大,同时所需要的效能表现又更加刁钻。

至于中国的业者也不应该被排除在外,毕竟2025年还有一段时日,美中的冲突也存在解除的可能性。

结语

整体来说,半导体微缩制程再往下走到2nm已是即将发生的事实,而摩尔定律也还能再继续维持下去,人们也将继续感受到电子装置与科技应用不断创新的便利性,尤其是在运算与AI处理的体验上。唯一的问题,就是这超级庞大的制造成本究竟有多少人可以负担。所以可以想见的是,再往下探的微缩制程可能不再具备多少意义,先进的半导体整合与异质设计,可能才是日后芯片开发者需要关注的所在。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3117内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!