Chiplet时代,如何玩转DRAM?

2023-05-08

13:41:36

来源: 互联网

点击

近年来,摩尔定律的放缓促使芯片行业为提升芯片性能做出了很多的尝试,Chiplet无疑是其中最受关注的一个选择。华邦电子次世代内存产品营销企划经理曾一峻先生对此也表示认同,并认为Chiplet的普及是一个必然的趋势。

如他所说,出于成本的考量,不是所有的集成芯片(如interface芯片,IO芯片,甚至是主芯片)都需要用到5纳米、3纳米那么先进的制程。如果可以让不同功能的芯片采用不同的制程——如针对运算的部分采用5纳米,一些IO芯片可能只需要7纳米或者12纳米,SoC成本结构上就会降低。这也正是Chiplet所推动的,也是其存在的重要价值。但是,如何将不同制程的芯粒连接起来,也就成为了头等大事,这也正是UCIe联盟成立所致力于解决的问题。

作为一家行业领先的DRAM供应商,华邦也加入了加入 UCIe 联盟,从DRAM角度,为Chiplet的普及添砖加瓦。

Chiplet面临的挑战

从定义上看,Chiplet一般是指预制好的、具有特定功能的、可用来组合集成的芯片(也叫芯粒),其技术重点在于将不同的芯片连接在一起并进行封装。需要强调的是,虽然经常和先进封装混为一谈,但其实Chiplet与先进封装是两个不同的概念。但是,我们又必须承认的是,行业内大多数的Chiplet 是通过先进封装技术将不同工艺制造的芯片进行集成的。

然而在采用 2.5D/3D 这样的垂直堆叠方式集成 Chiplet 芯片时,将面临几大关键挑战:

1.封装技术:随着业界对小型化的需求愈演愈烈,芯片必须保证在更小的封装空间内对更小尺寸的Chiplet 芯片进行封装,因此对封装技术的要求极高。

2.连接设计:芯片堆叠的顺序、走线方式都会影响合封芯片的性能,因此需要最佳的设计方式来降低整体风险。

3.热管理:将芯片堆叠在一起后,散热问题更为严峻,高温会影响芯片的性能与寿命,因此需要采取更尖端的散热技术来避免高温导致的性能下降甚至是封装失效。

另一方面,合封后的系统级芯片性能与集成在其中的 Chiplet 芯片性能息息相关。因此必须采用具备如下特质的裸片才能保证最终的芯片性能。

1.高度可靠:尽管在单个 Chiplet 芯片良率高达 98%的情况下,合封后的产品良率也会大幅下降,此外还可能会与其他芯片相互干扰,但提升裸片(die)的可靠性仍旧可在某种程度上提升合封芯片的可靠性;

2.散热合理:合封后,每个裸片与外界进行热传递的面积急剧缩小,发热量会进一步提高,因此必须尽可能降低裸片本身的散热,才能将合封芯片的发热控制在合理范围内;

3.高温稳定:合封芯片的发热远高于单一裸片的发热量,为此,裸片需要具备较好的高温下稳定性,才能保证芯片性能在温度升高的环境中不受损。

4.更低功耗:系统级芯片的功耗受 Chiplet 芯片的功耗影响极大,为满足应用得低功耗需求,需要一步降低裸片的自身功耗;

具体到DRAM方面,众所周知,随着人工智能等应用的火热,在芯片上合封更多的DRAM成为了行业的大势所趋。然而,正如曾一峻所说,要将DRAM合封在chiplet上,就需要兼容很多个接口协议(protocol),这不像单一颗芯片那么简单,所以做好完整的模拟是非常有必要的。只有这样做,才能避免由于不同制程上的差异造成的信号偏移。这也将是产业面对的另一个重大挑战。

依赖于公司在TSV和3D DRAM等方面积累的经验,华邦正在致力于帮助客户解决这个问题。

华邦的DRAM组合拳

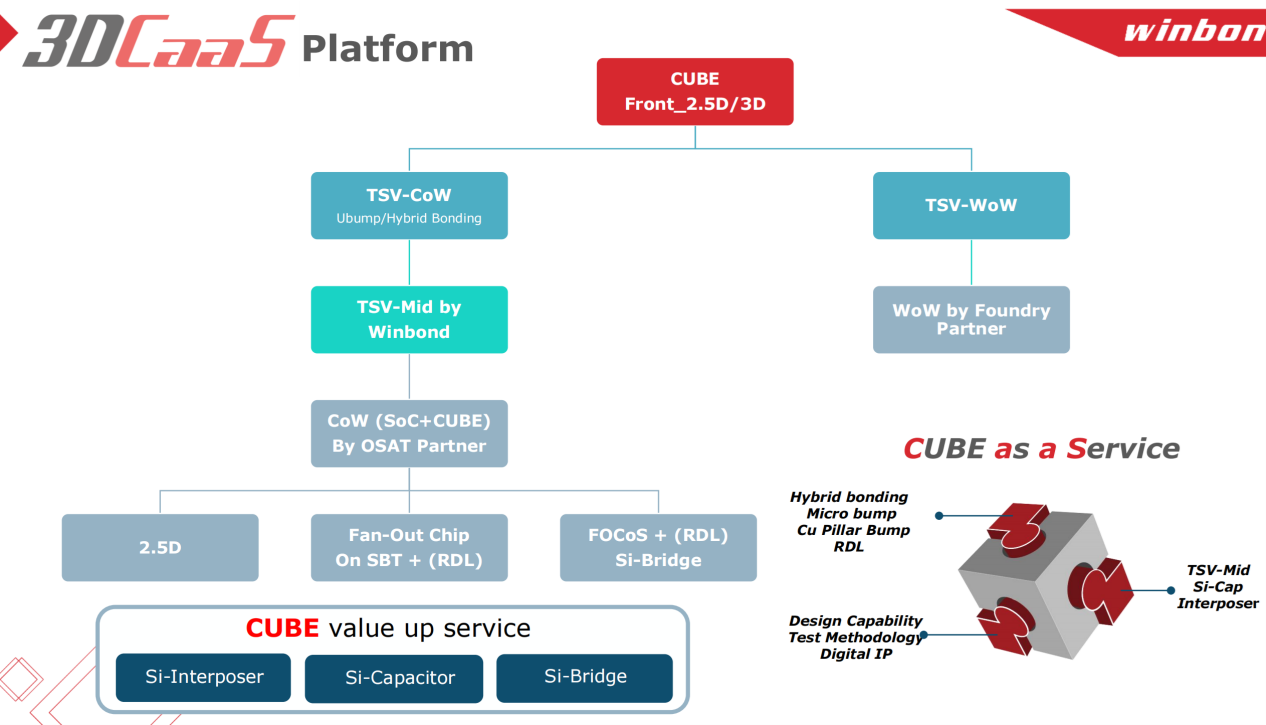

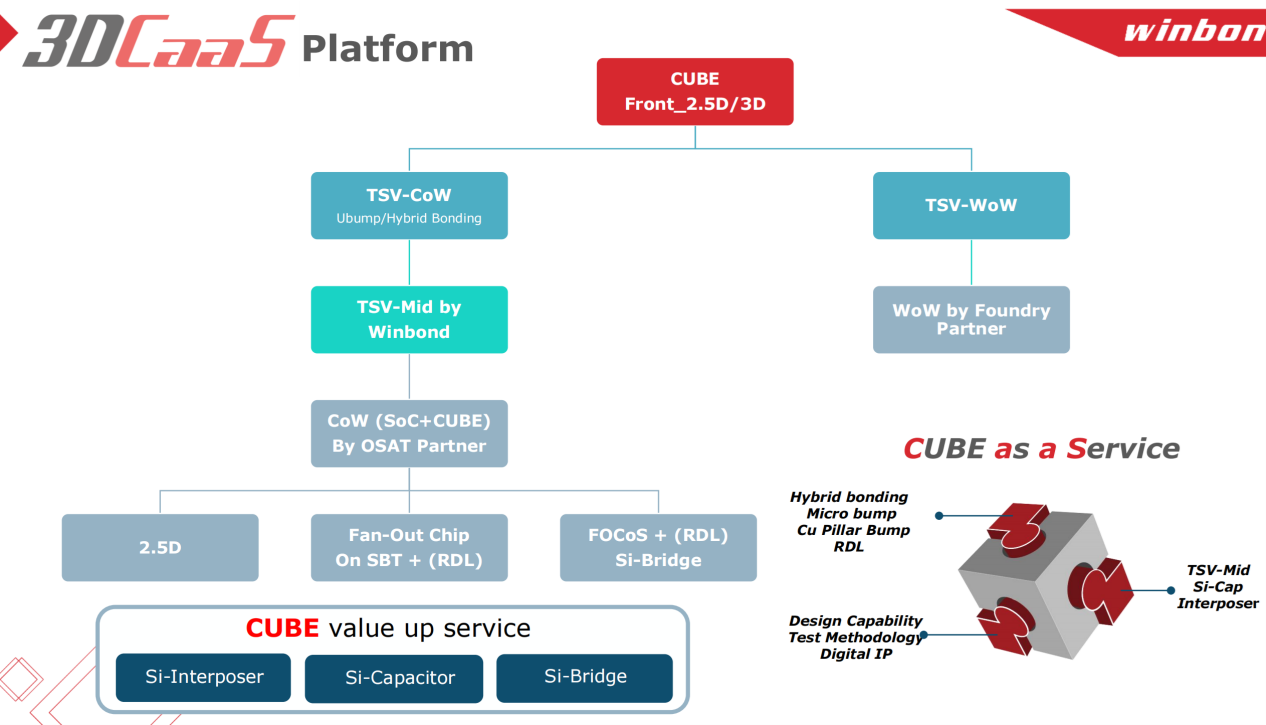

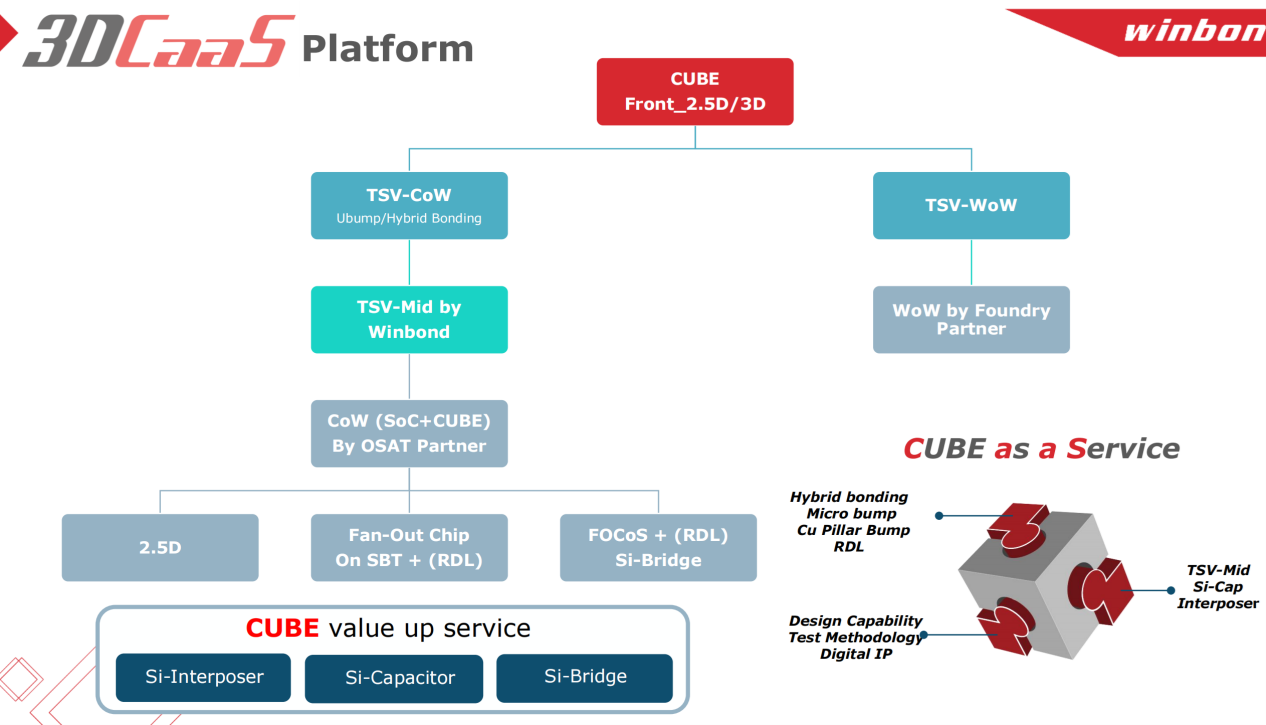

在早前宣布加入UCIe联盟的时候华邦就表示,公司将提供 3DCaaS(3D CUBE as a Service)一站式服务平台,为客户提供领先的标准化产品解决方案。他们指出,通过此平台,客户不仅可以获得 3D TSV DRAM(又名 CUBE)KGD 内存芯片和针对多芯片设备优化的 2.5D/3D 后段工艺(采用 CoW/WoW技术),还可获取由华邦的平台合作伙伴提供的技术咨询服务。这意味着客户可轻松获得完整且全面的 CUBE 产品支持,并享受 Silicon-Cap、interposer 等技术的附加服务。

当中,CUBE正是华邦这个服务的核心之一。

据曾一峻介绍,所谓CUBE,是Customized/Compact Ultra Bandwidth Elements,也就是半定制化的紧凑超高带宽DRAM。这是华邦针对当前SoC在DRAM合封上碰到的难题而推出的一个产品。

他解析说,目前市场上有些CPU为了增加高速缓存能效,直接增加SRAM的带宽和容量,但是这样的方式会增加非常高的成本。于是,为了节省成本,厂商会使用相对成熟制程的SRAM,例如5nm的 SoC裸片上堆叠7nm的SRAM 裸片。然而。但这种架构下,底部的CPU就需要埋入相当多的TSV,同时增加CPU裸片面积,成本依然会相对较高。

有见及此,针对边缘计算领域的需求,华邦将SoC裸片置上,而DRAM裸片置下,从而达到省去SoC的TSV工艺,如上图中虚线部分所示,这正是华邦CUBE的价值之一,这样的设计也能带来几个方面的优势:

一方面,SoC裸片尺寸就可以缩小,成本也会相应降低;另一方面,通过华邦的DRAM TSV工艺,可以将SoC的信号引至外部,使它们成为同一个封装芯片。“DRAM做TSV的好处是其裸片将会变得很薄,尺寸变得更小,这是CUBE解决方案的又一个优势。”曾一峻解析说。

再者,现在AI功能都有很高的算力需求,SoC裸片置上也可以带来更好的散热效果。因此,

“按照这样的方式进行3D 堆叠以及CUBE DRAM 裸片堆叠可以带来高带宽、低功耗和优秀的散热表现。因此在边缘计算处理器方面,华邦的CUBE解决方案主要面向的是低功耗、高带宽,以及稍微中低容量的内存需求,而TSV带来的好处就是SoC可以通过很短的信号线引致外部,整体的封装效果会更好。”曾一峻表示。

此外,因为CUBE芯片中还会提供硅电容(Si-Cap),这将有助于降低电源波动带来的影响。

曾一峻举例说,如果先进制程的SoC的核心电压只有0.75V-1V左右,并且运行过程中电源产生一些波动,除了会影响到功耗,还会影响信号的稳定性。但在硅电容容量提高的情况下,SoC借助硅电容就可以获得稳定的电压。

再者,由于中介层也是华邦所提供,因此客户在使用CUBE的时候能得到一个包括DRAM、中介层、硅电容在内的整体解决方案。这也是华邦加入UCIe后带来的贡献之一。

最后,相比于传统的引线键合(Wire Bonding),华邦CUBE的这种设计还可以在微键合(Micro Bonding)的情况下将1000微米的线长缩短至传统长度的2.5%——40微米。在未来的混合键合(Hybrid Bonding)封装工艺下,线长甚至可以缩短至1微米,进而降低功耗。

如前面所说,在打造了CUBE的基础上,华邦成立了3D CaaS平台,也就是CUBE as a Service。对于客户来说,这意味着华邦不仅仅提供DRAM裸片,而是包括一整套的解决方案。

华邦表示,无论是TSV、还是WOW(Wafer on Wafer),华邦都已经达成了与业内相关企业的合作,构建了合作伙伴生态。在COW(Chip on Wafer)方面,华邦也将提供TSV的DRAM裸片,并且会帮助SoC客户通过适合的合作伙伴进行后续封测。

在COW方面,华邦还提供了2.5D、Fan-Out以及3D堆叠工艺,其中2.5D和3D堆叠所用到的硅中介层华邦就可以提供,并且华邦的硅电容还能使芯片的SI/PI减小,使能耗表现更好,甚至华邦的Si-Bridge还能让硅中介层的裸片尺寸更小。

值得一提的是,目前市场上大多产品工艺都以普通封装为主,而华邦在利基型内存领域的业务主要是以KGD为主。基于这些深厚的经验积累,华邦将这个技术应用到CUBE这个中,推出了KGD 2.0产品。

据介绍,华邦在KGD 2.0的TSV的深宽比能力(也就是aspect Ratio)可以做到1:10,目前可以实现50微米的深度,相当于需要将芯片打磨至2 mil。未来,通过Hybrid Bonding工艺,华邦则能进一步可以实现1 微米的距离。而在全新的工艺下,KGD 2.0的信号完整性/电源完整性(SI/PI)表现也会更好,并且功耗会更低,可以低于LPDDR4的四分之一(为8pJ/Byte),而带宽可以实现16-256GB/s。

综上,华邦不仅可以提供完整的一站式解决方案,可以帮助客户解决从DRAM到封装测试再到IP等等一系列问题。得益于这个设计,如下图所示,华邦的这个方案在AI-ISP和CPU的设计中能够给客户提供更好的替代方案。

曾一峻透露,目前华邦就CUBE解决方案已经和几家客户在边缘计算和生成式AI这两个方向上展开了项目洽谈,展望未来,公司这个技术会寻找到更好的成长空间。

深厚的积累是底气

华邦能够面向Chiplet需求推出了极具竞争力的产品,其过去多年来在DRAM开发和产能上的布局是功不可没。

相对于市场上的三大内存厂商(三星、SK海力士和美光)而言,华邦主要专注于不需要非常先进的制程利基型内存,产品容量一般最大为8GB。

曾一峻表示,内存产品的制程实际上取决于容量,例如小容量的产品,SDRAM、DDR1、DDR2,使用46nm、65nm的制程绰绰有余。对于1Gb、2Gb、4Gb等容量,华邦会将其演进到25nm、25Snm,以及即将量产的20nm。通过这些制程来实现上述的容量在业界非常具备成本竞争力,这也让华邦目前的制程所聚焦的产品在成本和性价比方面都非常优秀。

基于这些产品,再加上公司在产能上的布局,华邦能够为客户提供持续稳定、可靠的服务。

据介绍。华邦目前拥有两座12寸晶圆厂,当中就包括了Flash和DRAM产线各一条的台中的Fab 6工厂,该厂的中小容量DRAM制程会维持在65nm、46nm以及38nm、25nm,不会再向着更小的制程演进,而是专注于成熟制程产品。

此外,从去年的下半年开始,华邦在高雄新建的第二座厂已经正式量产包括2GB和4GB产品在内的25nmDRAM。其投片量达到了1万片/月左右。后续,华邦会将其高雄厂规划的产能会提升到1.4万片至2万片/月。“高雄厂所开发的20nm产品在今年中也会进入量产阶段,下一步会向19nm制程演进。”曾一峻说。

在这些极具竞争力的产品和产能的支持下,华邦电子在Chiplet时代发挥的作用是可以预见的。华邦DRAM 产品事业群副总范祥云更是直言:“随着 UCIe 规范的普及,相信CUBE将在云端到边缘端的人工智能应用中充分发挥潜力,扮演更加重要的角色。”

如他所说,出于成本的考量,不是所有的集成芯片(如interface芯片,IO芯片,甚至是主芯片)都需要用到5纳米、3纳米那么先进的制程。如果可以让不同功能的芯片采用不同的制程——如针对运算的部分采用5纳米,一些IO芯片可能只需要7纳米或者12纳米,SoC成本结构上就会降低。这也正是Chiplet所推动的,也是其存在的重要价值。但是,如何将不同制程的芯粒连接起来,也就成为了头等大事,这也正是UCIe联盟成立所致力于解决的问题。

作为一家行业领先的DRAM供应商,华邦也加入了加入 UCIe 联盟,从DRAM角度,为Chiplet的普及添砖加瓦。

Chiplet面临的挑战

从定义上看,Chiplet一般是指预制好的、具有特定功能的、可用来组合集成的芯片(也叫芯粒),其技术重点在于将不同的芯片连接在一起并进行封装。需要强调的是,虽然经常和先进封装混为一谈,但其实Chiplet与先进封装是两个不同的概念。但是,我们又必须承认的是,行业内大多数的Chiplet 是通过先进封装技术将不同工艺制造的芯片进行集成的。

然而在采用 2.5D/3D 这样的垂直堆叠方式集成 Chiplet 芯片时,将面临几大关键挑战:

1.封装技术:随着业界对小型化的需求愈演愈烈,芯片必须保证在更小的封装空间内对更小尺寸的Chiplet 芯片进行封装,因此对封装技术的要求极高。

2.连接设计:芯片堆叠的顺序、走线方式都会影响合封芯片的性能,因此需要最佳的设计方式来降低整体风险。

3.热管理:将芯片堆叠在一起后,散热问题更为严峻,高温会影响芯片的性能与寿命,因此需要采取更尖端的散热技术来避免高温导致的性能下降甚至是封装失效。

另一方面,合封后的系统级芯片性能与集成在其中的 Chiplet 芯片性能息息相关。因此必须采用具备如下特质的裸片才能保证最终的芯片性能。

1.高度可靠:尽管在单个 Chiplet 芯片良率高达 98%的情况下,合封后的产品良率也会大幅下降,此外还可能会与其他芯片相互干扰,但提升裸片(die)的可靠性仍旧可在某种程度上提升合封芯片的可靠性;

2.散热合理:合封后,每个裸片与外界进行热传递的面积急剧缩小,发热量会进一步提高,因此必须尽可能降低裸片本身的散热,才能将合封芯片的发热控制在合理范围内;

3.高温稳定:合封芯片的发热远高于单一裸片的发热量,为此,裸片需要具备较好的高温下稳定性,才能保证芯片性能在温度升高的环境中不受损。

4.更低功耗:系统级芯片的功耗受 Chiplet 芯片的功耗影响极大,为满足应用得低功耗需求,需要一步降低裸片的自身功耗;

具体到DRAM方面,众所周知,随着人工智能等应用的火热,在芯片上合封更多的DRAM成为了行业的大势所趋。然而,正如曾一峻所说,要将DRAM合封在chiplet上,就需要兼容很多个接口协议(protocol),这不像单一颗芯片那么简单,所以做好完整的模拟是非常有必要的。只有这样做,才能避免由于不同制程上的差异造成的信号偏移。这也将是产业面对的另一个重大挑战。

依赖于公司在TSV和3D DRAM等方面积累的经验,华邦正在致力于帮助客户解决这个问题。

华邦的DRAM组合拳

在早前宣布加入UCIe联盟的时候华邦就表示,公司将提供 3DCaaS(3D CUBE as a Service)一站式服务平台,为客户提供领先的标准化产品解决方案。他们指出,通过此平台,客户不仅可以获得 3D TSV DRAM(又名 CUBE)KGD 内存芯片和针对多芯片设备优化的 2.5D/3D 后段工艺(采用 CoW/WoW技术),还可获取由华邦的平台合作伙伴提供的技术咨询服务。这意味着客户可轻松获得完整且全面的 CUBE 产品支持,并享受 Silicon-Cap、interposer 等技术的附加服务。

当中,CUBE正是华邦这个服务的核心之一。

据曾一峻介绍,所谓CUBE,是Customized/Compact Ultra Bandwidth Elements,也就是半定制化的紧凑超高带宽DRAM。这是华邦针对当前SoC在DRAM合封上碰到的难题而推出的一个产品。

他解析说,目前市场上有些CPU为了增加高速缓存能效,直接增加SRAM的带宽和容量,但是这样的方式会增加非常高的成本。于是,为了节省成本,厂商会使用相对成熟制程的SRAM,例如5nm的 SoC裸片上堆叠7nm的SRAM 裸片。然而。但这种架构下,底部的CPU就需要埋入相当多的TSV,同时增加CPU裸片面积,成本依然会相对较高。

有见及此,针对边缘计算领域的需求,华邦将SoC裸片置上,而DRAM裸片置下,从而达到省去SoC的TSV工艺,如上图中虚线部分所示,这正是华邦CUBE的价值之一,这样的设计也能带来几个方面的优势:

一方面,SoC裸片尺寸就可以缩小,成本也会相应降低;另一方面,通过华邦的DRAM TSV工艺,可以将SoC的信号引至外部,使它们成为同一个封装芯片。“DRAM做TSV的好处是其裸片将会变得很薄,尺寸变得更小,这是CUBE解决方案的又一个优势。”曾一峻解析说。

再者,现在AI功能都有很高的算力需求,SoC裸片置上也可以带来更好的散热效果。因此,

“按照这样的方式进行3D 堆叠以及CUBE DRAM 裸片堆叠可以带来高带宽、低功耗和优秀的散热表现。因此在边缘计算处理器方面,华邦的CUBE解决方案主要面向的是低功耗、高带宽,以及稍微中低容量的内存需求,而TSV带来的好处就是SoC可以通过很短的信号线引致外部,整体的封装效果会更好。”曾一峻表示。

此外,因为CUBE芯片中还会提供硅电容(Si-Cap),这将有助于降低电源波动带来的影响。

曾一峻举例说,如果先进制程的SoC的核心电压只有0.75V-1V左右,并且运行过程中电源产生一些波动,除了会影响到功耗,还会影响信号的稳定性。但在硅电容容量提高的情况下,SoC借助硅电容就可以获得稳定的电压。

再者,由于中介层也是华邦所提供,因此客户在使用CUBE的时候能得到一个包括DRAM、中介层、硅电容在内的整体解决方案。这也是华邦加入UCIe后带来的贡献之一。

最后,相比于传统的引线键合(Wire Bonding),华邦CUBE的这种设计还可以在微键合(Micro Bonding)的情况下将1000微米的线长缩短至传统长度的2.5%——40微米。在未来的混合键合(Hybrid Bonding)封装工艺下,线长甚至可以缩短至1微米,进而降低功耗。

如前面所说,在打造了CUBE的基础上,华邦成立了3D CaaS平台,也就是CUBE as a Service。对于客户来说,这意味着华邦不仅仅提供DRAM裸片,而是包括一整套的解决方案。

华邦表示,无论是TSV、还是WOW(Wafer on Wafer),华邦都已经达成了与业内相关企业的合作,构建了合作伙伴生态。在COW(Chip on Wafer)方面,华邦也将提供TSV的DRAM裸片,并且会帮助SoC客户通过适合的合作伙伴进行后续封测。

在COW方面,华邦还提供了2.5D、Fan-Out以及3D堆叠工艺,其中2.5D和3D堆叠所用到的硅中介层华邦就可以提供,并且华邦的硅电容还能使芯片的SI/PI减小,使能耗表现更好,甚至华邦的Si-Bridge还能让硅中介层的裸片尺寸更小。

值得一提的是,目前市场上大多产品工艺都以普通封装为主,而华邦在利基型内存领域的业务主要是以KGD为主。基于这些深厚的经验积累,华邦将这个技术应用到CUBE这个中,推出了KGD 2.0产品。

据介绍,华邦在KGD 2.0的TSV的深宽比能力(也就是aspect Ratio)可以做到1:10,目前可以实现50微米的深度,相当于需要将芯片打磨至2 mil。未来,通过Hybrid Bonding工艺,华邦则能进一步可以实现1 微米的距离。而在全新的工艺下,KGD 2.0的信号完整性/电源完整性(SI/PI)表现也会更好,并且功耗会更低,可以低于LPDDR4的四分之一(为8pJ/Byte),而带宽可以实现16-256GB/s。

综上,华邦不仅可以提供完整的一站式解决方案,可以帮助客户解决从DRAM到封装测试再到IP等等一系列问题。得益于这个设计,如下图所示,华邦的这个方案在AI-ISP和CPU的设计中能够给客户提供更好的替代方案。

曾一峻透露,目前华邦就CUBE解决方案已经和几家客户在边缘计算和生成式AI这两个方向上展开了项目洽谈,展望未来,公司这个技术会寻找到更好的成长空间。

深厚的积累是底气

华邦能够面向Chiplet需求推出了极具竞争力的产品,其过去多年来在DRAM开发和产能上的布局是功不可没。

相对于市场上的三大内存厂商(三星、SK海力士和美光)而言,华邦主要专注于不需要非常先进的制程利基型内存,产品容量一般最大为8GB。

曾一峻表示,内存产品的制程实际上取决于容量,例如小容量的产品,SDRAM、DDR1、DDR2,使用46nm、65nm的制程绰绰有余。对于1Gb、2Gb、4Gb等容量,华邦会将其演进到25nm、25Snm,以及即将量产的20nm。通过这些制程来实现上述的容量在业界非常具备成本竞争力,这也让华邦目前的制程所聚焦的产品在成本和性价比方面都非常优秀。

基于这些产品,再加上公司在产能上的布局,华邦能够为客户提供持续稳定、可靠的服务。

据介绍。华邦目前拥有两座12寸晶圆厂,当中就包括了Flash和DRAM产线各一条的台中的Fab 6工厂,该厂的中小容量DRAM制程会维持在65nm、46nm以及38nm、25nm,不会再向着更小的制程演进,而是专注于成熟制程产品。

此外,从去年的下半年开始,华邦在高雄新建的第二座厂已经正式量产包括2GB和4GB产品在内的25nmDRAM。其投片量达到了1万片/月左右。后续,华邦会将其高雄厂规划的产能会提升到1.4万片至2万片/月。“高雄厂所开发的20nm产品在今年中也会进入量产阶段,下一步会向19nm制程演进。”曾一峻说。

在这些极具竞争力的产品和产能的支持下,华邦电子在Chiplet时代发挥的作用是可以预见的。华邦DRAM 产品事业群副总范祥云更是直言:“随着 UCIe 规范的普及,相信CUBE将在云端到边缘端的人工智能应用中充分发挥潜力,扮演更加重要的角色。”

责任编辑:sophie