国产硬件仿真混合验证平台,深度解读

2023-07-27

16:33:33

来源: 互联网

点击

软件仿真(Simulation),原型验证(Prototyping),以及硬件仿真 (Emulation),是当前主要的三种有效的验证方法,在芯片前端设计的功能性验证阶段起到了关键的作用。

近年来,由于大数据处理和AI芯片设计规模的扩大,以及市场竞争激烈导致的快速迭代需求,越来越多的芯片设计公司开始选择硬件仿真,以提高芯片验证效率,缩短芯片开发周期。

相较于软件仿真和原型验证,硬件仿真具有可支持设计容量大、扩展性好、工程构建时间短、仿真速度快、调试能力强、验证场景丰富等特点,适合大型设计从模块级、芯片级到系统级的仿真验证。

硬件仿真验证模式

硬件仿真支持的丰富的验证模式,可以满足芯片设计不同阶段的验证需求,常用于架构设计、前期开发、模块开发、IP开发、系统深度调试等芯片开发阶段。

常见的仿真验证模式,主要包括:电路内仿真(In-Circuit Emulation,ICE仿真),事务级的仿真加速(Transaction Based Acceleration,TBA仿真),以及混合仿真(QEMU)等。在不同的芯片设计阶段,可以选择合适的仿真加速方法,来提升验证效率。

电路内仿真(In-Circuit Emulation,ICE仿真)

电路内仿真是使用在线仿真器(In-Circuit Emulator)进行具有特定调试技术的硬件仿真加速,其中在线仿真器代替实际硬件以便在实际系统环境中运行和测试。此方法允许工程师在实际的系统环境中进行测试和调试,而无需等待硬件原型的生产。这可以大大加速开发过程,并提高最终产品的质量。

事务级的仿真加速(Transaction Based Acceleration,TBA仿真)

事务级的仿真加速是通过使用总线功能模型Bus Functional Model (BFM),将运行在软件上的Testbench和运行在硬件仿真系统中的DUT进行事务级层面的软硬联合验证。即在主机上运行的Testbench和在硬件仿真上运行的DUT是通过无时序的事物进行交互。通过这种方法,仿真速度可以大大提高,因为仿真的焦点从每个时钟周期的具体操作转移到了更高级别的事务。这种方法常用于大规模系统的设计验证,可以提高仿真的效率。

混合仿真(Hybrid Emulation)

混合仿真是将硬件仿真与软件仿真相结合,允许工程师同时观察和调试系统的硬件和软件部分。混合仿真可以提供对整个系统的全面视图,并可以在更高的抽象级别进行仿真,可以进一步提高仿真速度和效率。是IC设计团队在早期架构优化、软硬件协同开发、RTL级仿真验证中的重要验证方法。

这些验证模式都是硬件仿真的一部分或者扩展,它们提供了不同层次和粒度的仿真和验证能力,以适应不同的设计需求和验证目标。在实际的设计和验证过程中,工程师可能会根据需要选择适合的仿真方法。

混合仿真(QEMU)

QEMU

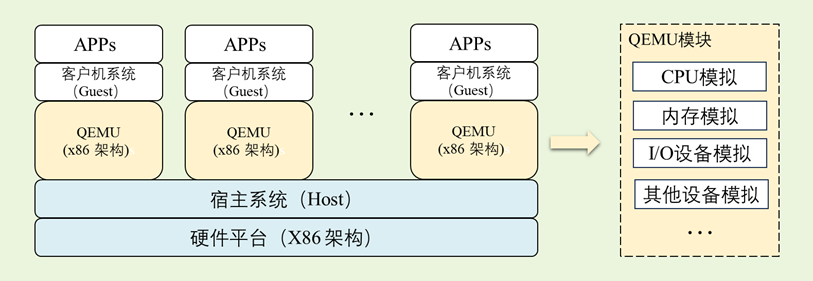

QEMU是纯软件实现的一个开源、跨平台的虚拟化模拟器,几乎可以模拟任何硬件设备。通常是模拟一台能够独立运行操作系统的虚拟机,混合仿真时虚拟机会以为自己和真实硬件进行数据交互,而该“硬件”实际上却是QEMU模拟,QEMU 将这些指令转译给真正的硬件。本质上,虚拟出的每个虚拟机对应宿主系统(Host)上的一个QEMU进程,而虚拟机的执行线程(如 CPU 线程、I/O 线程等)对应QEMU进程的一个线程。

图1 QEMU架构图

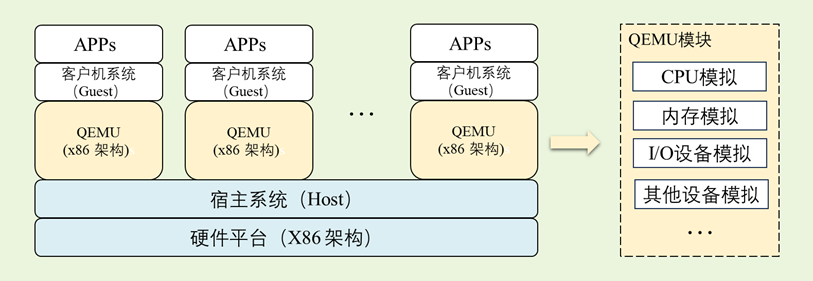

SystemC

SystemC是一个支持系统建模的开源的C++ library。混合仿真验证前,通常优先开发抽象SystemC模型(如TLM模型),然后将此模型转化为RTL并基于此模型上开发软件。在此过程中,软硬件的诸多错误能尽早被发现,从而节省开发时间。使用QEMU和SystemC可以共同组成虚拟验证平台,实现SoC系统级建模。

图2 SystemC Simulation

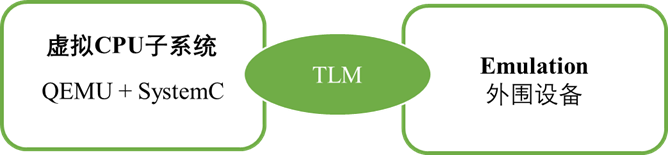

基于QEMU的混合仿真验证

混合验证是一种方法,它在使用硬件仿真进行DUT仿真的同时,利用虚拟原型建立目标SoC环境,并进行相应软硬件的协同开发调试。混合仿真是IC设计团队在早期架构优化、软硬件协同开发、RTL级仿真验证中的重要工具。

基于QEMU和硬件仿真系统的混合仿真,是在硬件仿真系统和QEMU上同时运行SoC的不同设计模块,在SoC整体架构硬件实现之前提供嵌入式软件和硬件的协同仿真,为系统架构的优化、RTL的早期开发、以及嵌入式软件开发,提供准确,即时的仿真验证环境,有力推动产品开发周期左移,从而加速SoC的研发进程。

QEMU运行在Runtime Server上,一般通过SystemC实现TLM(Transaction Level Model)模型,提供虚拟CPU、Linux内核以及用户态程序。QEMU通过标准SCEMI协议和硬件仿真器通信,硬件仿真器上可运行SOC外设等IP,从而实现完整的混合仿真环境。

图3 QEMU混合仿真

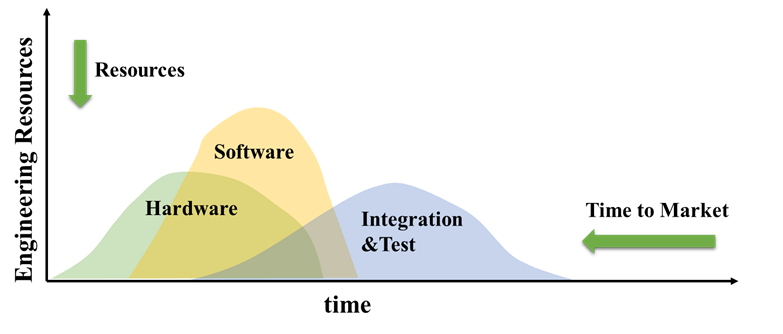

混合仿真带来的好处

混合仿真带来了诸多好处,主要表现在软件开发和集成测试的工作可以大幅度提前,显著地缩短了项目周期。在应用混合验证之前,软硬件开发和集成测试往往要等待硬件设计完成后才能开始,这将会导致项目周期延长。而在使用混合验证之后,软硬件开发和集成测试可以在硬件设计阶段同时进行,这样将会显著地缩短整个项目周期。

图4 使用混合验证前

图5 使用混合验证后

基于OmniArk和QEMU的混合仿真

思尔芯自主研发的OmniArk芯神鼎硬件仿真系统,采用超大规模可扩展阵列架构设计,设计容量最大10亿门。支持TBA、ICE 、混合仿真等多种仿真验证模式,可以满足不同验证场景需求。

图6 OmniArk芯神鼎硬件仿真系统

思尔芯提供的混合验证解决方案,通过连接开源虚拟机QEMU工具和OmniArk芯神鼎硬件仿真系统,实现了虚拟原型硬件和嵌入式软件协同混合验证,为早期的设计架构的验证优化、嵌入式软件的协同开发、RTL级的仿真加速提供更准确、更及时的仿真验证环境。

以混合仿真一个SoC芯片设计为例。SoC整体系统架构如下图所示,主要由ARMv8 CPU、AMBA BUS、NVDLA和DRAM等模块组成。为了实现QEMU虚拟平台与OmniArk芯神鼎硬件仿真系统的混合仿真,我们将NVDLA和DRAM移植到OmniArk芯神鼎硬件仿真系统中进行仿真,同时使用QEMU实现ARMv8的软件模型。

图7 SoC系统框图

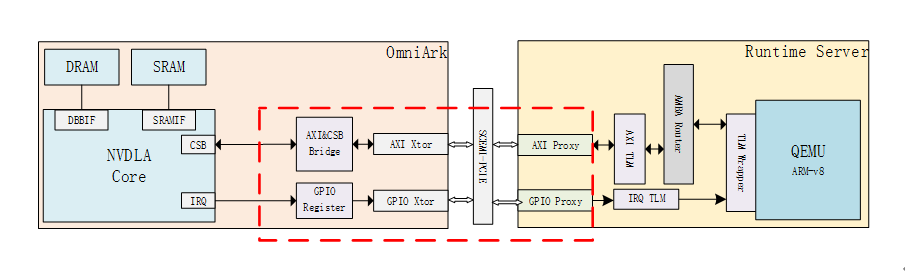

在设计移植到OmniArk芯神鼎硬件仿真系统后,Runtime Server端采用QEMU模拟运行ARMv8,并通过TLM Wrapper将其挂载到AMBA总线上。OmniArk芯神鼎硬件仿真系统仿真运行NVDLA,通过AXI Transactor(简称Xtor)、GPIO Transactor挂载到AMBA总线上。Runtime Server和OmniArk芯神鼎硬件仿真系统之间通过SCE-MI协议进行软硬件协同仿真。

图8 QEMU混合仿真系统框图

TLM Wrapper,建立一套基于TLM模型的通信机制,将QEMU包装成TLM模型,使QEMU模拟的设备能够与SystemC开发的模块进行通信。

AMBA Router,以软件形式模拟AMBA总线,实现了标准的AMBA路由机制和仲裁机制,可将多个TLM模型连接并进行数据通信。

AXI TLM,是一个基于AXI总线的TLM模型,负责将AXI接口设备适配到AMBA Router总线上。

IRQ TLM,则是中断TLM模型,负责将设备的中断信号经TLM2C发送给QEMU模拟的CPU,由CPU作出响应处理。

总结

当前,许多全流程验证工作都依赖于硬件仿真来完成。在早期,硬件仿真主要被用于代码设计的后端阶段,主要用于确认代码功能的正确性。然而,随着设计流程时间需求的加剧,更多的步骤开始被集成到硬件仿真中,包括早期的功耗分析、系统环境构建和逻辑调试等。

同时,硬件仿真系统的专用化趋势日益显著。对于那些需要处理大量数据,但算法相对单一的应用领域,例如加密算法和WIFI应用等,他们对仿真的需求正在逐步增大。在芯片设计过程中,根据设计的复杂性和特性,可能需要采用不同的仿真验证模式。在芯片设计中,我们可能需要不同的仿真验证模式以适应不同的设计复杂性和特性。因此,专用的硬件仿真技术提供了强大的支持,使硬件仿真具有更高的灵活性和适应性,满足各种不同场景和需求的验证任务。

思尔芯自主研发的OmniArk芯神鼎硬件仿真系统,正是这种具有更高灵活性和适应性的硬件仿真系统,目前已在多个芯片设计企业成功使用。产品除了支持TBA、ICE 、混合仿真等多种仿真验证模式外,还支持用户设计的快速导入和全自动快速编译、可以支持高速的仿真运行速度,同时具备强大的调试能力和对海量的数据处理能力,可以快速寻找和修复源代码中潜在的深度错误和性能瓶颈。利用这个平台,用户可以更高效地进行芯片设计和优化,极大地提高了芯片设计的质量和效率。

欢迎下载白皮书《基于OmniArk芯神鼎硬件仿真系统和QEMU的混合验证平台》。

下载方式:点击文章左下角【阅读原文】即可下载。

更多白皮书,可登录思尔芯官网www.s2ceda.com点击“热门资源-技术文档”下载。

关于思尔芯 S2C

思尔芯(S2C)自2004年设立上海总部以来始终专注于集成电路EDA领域。作为业内知名的EDA解决方案专家,公司业务已覆盖架构设计、软件仿真、硬件仿真、原型验证、验证云服务等工具。已与超过600家国内外企业建立了良好的合作关系,服务于人工智能、高性能计算、图像处理、数据存储、信号处理等数字电路设计功能的实现,广泛应用于物联网、云计算、5G通信、智慧医疗、汽车电子等终端领域。

公司总部位于上海,并建立了全球化的技术研发与市场服务网络,在北京、深圳、西安、香港、东京、首尔及圣何塞等地均设有分支机构或办事处。

思尔芯在EDA领域的技术实力受到了业界的广泛认可,通过多年耕耘,已在数字前端EDA领域构筑了技术与市场的双优势地位。并参与了我国EDA团体标准的制定,承担了多项国家及地方重大科研项目,获评为国家级专精特新“小巨人”企业。

了解更多详情,请访问www.s2ceda.com

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 数字时代下的视听行业,西部数据正扮演重要角色

- 2 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 3 研发收关:进迭时空高性能处理器核X100产品发布会震撼来袭

- 4 广东场效应半导体,二十多年坚持做一件事