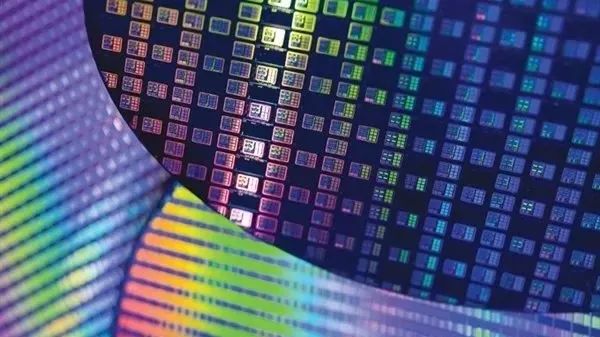

EUV微影技术进入量产最后冲刺阶段

来源:内容来自eettaiwan,谢谢。

随着工程师们竞相解决错综复杂的相关问题,酝酿了20年的新世代微影工具终于来到大量问世前的最后一个阶段──尽管极紫外光(EUV)步进机的大量生产面临复杂的问题以及紧迫的时间,专家们仍然抱持乐观态度。

好消息是,半导体产业界正众志成城、积极推动技术进展;如比利时研究机构Imec的技术与系统执行副总裁An Steegen所言:「在过去,可能会有一家公司率先采用最新的半导体技术,但现在几乎所有的逻辑制程技术供应商都跳进来、咬紧牙关努力并勇于承担风险。」

Imec是荷兰EUV微影设备大厂ASML的长期合作伙伴,他们与晶圆代工厂、半导体供应商携手,现在的目标是解决该种有尺寸有一个房间大小、将用以制造新一代芯片的设备剩下的最后几个主要问题;Steegen在Imec年度技术论坛接受EE Times采访时指出,这很像是在2008年问世的FinFET电晶体,是很重大但充满挑战的半导体性能提升关键。

她表示:「人们比较过下世代节点的最糟情况以及旧节点的最佳情况,现在各方都同意FinFET是具备超高性能的元件;我学到的教训是要对所有事情抱持怀疑态度…未来的半导体制程技术还有足够进步空间,让SoC设计工程师能得到他们想要的。」

而在笔者于Imec总部排队等着喝咖啡时与一位有32年工作资历的EUV开发老将闲聊时,他简单表示:「现在有很多压力…但我们正在取得进展。」

确实,三星(Samsung)的晶圆代工部门赶着在今年底于7纳米制程导入EUV,该公司的目标是超越最大竞争对手台积电(TSMC),后者正利用现有的浸润式微影设备进行7纳米设计案的投片;台积电与另一家晶圆代工大厂GlobalFoundries也不落人后,他们打算在明年以EUV量产强化版的7纳米制程。

Imec预期,DRAM制造商会在D14+节点采用EUV技术──应该会在2021年记忆体半间距(half pitches)来到20纳米以下时。

目前Imec有两个技术开发重点,有助于舒缓边缘粗糙度(line-edge roughness)的问题,并消除所谓的随机效应(stochastics)、随机误差(random errors)等造成触点漏失(create missing) 、触点断续(kissing contacts)的缺陷。那些误差在今年稍早于对下一代5纳米节点十分关键的15纳米临界尺寸首度被发现,但研究人员表示他们也在7纳米看到一样的问题。

Steegen预期将会有混合式解决方案出现,这种方案会采用扫描机设定、光阻剂材料以及后期处理等方法的结合,以接续断裂的线路、将粗糙部分抹平或是填补漏失的触点。

晶圆代工业者可以提供更高剂量的EUV光源──例如80 millijoules/cm2──以扩大制程容许范围(process window),但这会让生产速度减慢;Steegen表示:「第一次实作时的最高剂量决定权在于各家晶圆代工厂。」

今天是《半导体行业观察》为您分享的第1603期内容,欢迎关注。

关注微信公众号 半导体行业观察(ID:icbank) ,后台回复以下关键词获取更多相关内容

联发科 | 摩尔定律 | 材料 | 面板 | 晶体管 | 开源 | 韦尔股份 | 封装 | 展会

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!

点击阅读原文了解摩尔精英

-

- 半导体行业观察

-

- 摩尔芯闻