FinFET工艺适合做毫米波电路吗?

2019-09-10

14:00:11

来源: 半导体行业观察

在高速接口(Serdes)方向,FinFET CMOS的工艺已经成为事实上的主流。

单通道56Gbps这一代应该大都采用16nm的FinFET,下一代112Gbps应该会采用7nm工艺。

这背后的道理有两个方面。

第一是高速接口本身的性能。

高速接口中数字电路的比重很大,采用FinFET工艺可减小芯片面积和功耗。

面积小一般也意味着寄生电容小,有利于提高速度。

第二是应用场景。

高速接口作为接口,为其他核心功能电路提供数据接入,没有脱离核心功能单独选择工艺的自由。

比如交换机、高性能计算等芯片,一般会在芯片四周密密麻麻的排布高速接口芯片,不存在异质集成的可能性。

毫米波电路情况不同。

毫米波以模拟电路为主,不需要很复杂的数字功能,与数字电路的接口较简单。

且毫米波电路里面大量用到电感、传输线等无源器件,而无源器件的面积是不随着工艺提高的变小的。

这也意味着,工艺越先进,单个无源器件的成本越高。

综合这些原因,用FinFET来做毫米波的优势没有高速串口那么清晰。

对于一个毫米波系统,至少有两种选择方案,第一种是毫米波和数字系统都使用FinFET工艺,享受单芯片集成的优势,但同时也要忍受FinFET较低的工作电压等等;

第二种是使用异质集成,选择FinFET来设计系统的数字部分,采用平面工艺(CMOS、SOI或SiGe)来对毫米波电路进行优化,最终在封装里面把两部分集成在一起。

这样毫米波部分的性能肯定更好,但封装的成本也会相对较高。

最终哪种方案胜出,我觉得主要决定于商业上而非技术上的因素,偶然性较大。

那么,FinFET本身到底适不适合做毫米波电路。

我找到几篇论文在讨论这一点,一篇来自于GlobalFoundries,一篇来自于Intel(Google关键词:

FinFET,RF,Millimeter Wave),在这里跟大家分享一下。

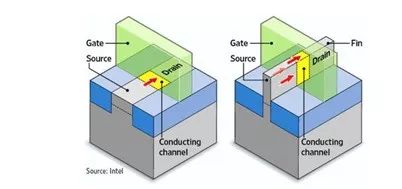

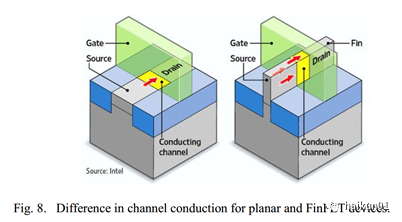

这个图给出了平面和FinFET晶体管的立体图。

左边是平面晶体管。

在晶体管的沟道长度越来越短的时候(上图中绿色栅极的厚度),人们发现,栅极对沟道电流的控制也在变差,沟道没法很好的关断,晶体管的漏电电流变得不可接受。

这一点很好理解,毕竟栅与沟道重合的区域也变得越来越少。

这时候FinFET这个很天才的解决方案出场了。

就像右图中画的,沟道向上长到栅极内部,这样一来,栅极电压可以从三个面来控制沟道电流。

在提高沟道控制这一点上,FinFET无疑是非常成功的,它至少把晶体管的漏电降低了几个数量级,开关速度也变得更快。

也正是因为FinFET对沟通控制能力加强,摩尔定律的Scaling Down这个游戏才能继续走下去,否则短沟道效应已经要失控了。

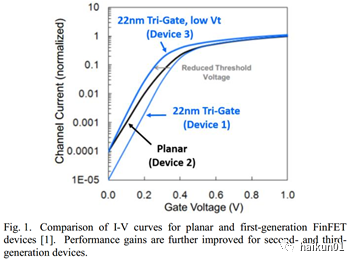

上图实测比较了两个FinFET晶体管(low Vt和high Vt)和一个平面晶体管。

比较1号晶体管和2号晶体管,FinFET和平面有相近的饱和区gm和Ion,但是FinFET的漏电电流小了一个数量级。

比较2号晶体管和3号晶体管,它们有相近的漏电电流,但FinFET晶体管有更高的饱和区gm,且在更小的栅端电压下就能开启,因而开关速度更快。

这对数字电路或者低功耗模拟电路都有很大的好处。

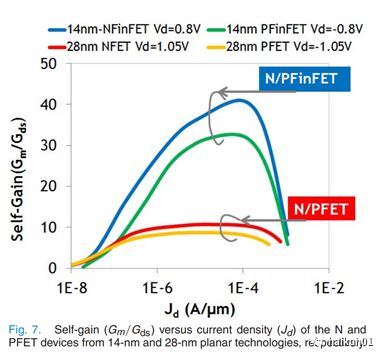

加强对沟道电流控制带来的另一个好处是降低了沟道调制效应,大幅提高了本征增益(gm*rout)。

GlobalFoundries比较了他们的14nmFinFET和28nm的平面CMOS,本征增益大概提高了快4倍。

上面这几个特点对低频模拟电路的好处比毫米波电路更大。

更小的栅电压就能开启,所以我可以用更低的电源电压;

本征增益更大,用更小的gm就能实现相同的增益。

这两点都能降低功耗。

毫米波电路我们还需要看截止频率(ft和fmax)和噪声表现。

FinFET工艺在ft和fmax方面的表现怎么样不那么直观。

Ft主要受栅端的寄生电容的影响。

比较FinFET和平面CMOS的栅端寄生电容的话,主要有几个因素:

栅的厚度减小导致电容变小;

栅和源漏的重叠增大导致电容变大;

FinFET栅极有一段多余的部分也会贡献寄生电容。

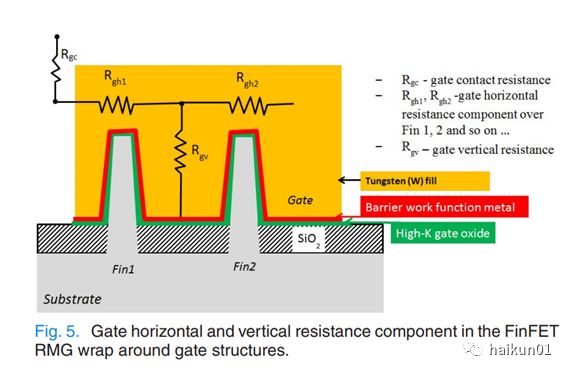

而Fmax受栅端寄生电阻的影响很大。

那么Scaling Down让底层金属越来越细还有栅的隆起都是会增大栅电阻的。

下面说一下几家代工厂论文里汇报的实测结果。

Intel的22nm FinFET有两个版本,分别针对ft和fmax优化,优化后的峰值ft是310GHz,峰值fmax是460GHz。

GlobalFoundries的14nm FinFET工艺的峰值ft和fmax分别是314GHz和227GHz。

Tsmc的16nm FinFET的峰值ft和fmax大约都在300GHz,但号称2020年的优化版本fmax能提高到380GHz。

另外,在实际设计中有两点值得注意:

一是截止频率还与FinFET的Fin数目取值有关,二是一般工艺厂在提取这些参数的时候会将低层金属寄生包括在内,当连线到高层金属时,这些数据还会再降一点。

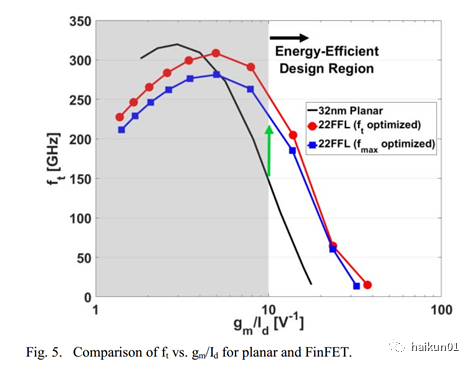

Intel比较了22nm FinFET和32nm平面工艺的截止频率跟垮导效率(gm/Id)的关系。

这个图的信息量很足。

首先,32nm的平面工艺截止频率的最大值是要高一点的,但它的峰值截止频率对应的gm/id在3左右,而FinFET的峰值截止频率的gm/id大约是5,这意味着FinFET的能量效率更高。

在gm/id大于10的区域,FinFET的截止频率要大于平面工艺。

这个信息对我们设计毫米波电路很有用。

在毫米波电路里,我们想要大的gm,又不想晶体管引入太大寄生电容,因此会把偏置电压设高一点(相当于提高gm/id)。

那这个图就告诉我们,如果使用FinFET设计毫米波电路,偏置电压相比于平面工艺应该低一点。

噪声性能直接放结论吧,FinFET的噪声性能比平面工艺更好,无论是热噪声还是Flicker噪声。

这一点几篇论文的结论都是一致的。

1)FinFET对于数字电路和低频模拟电路加成明显;

2)对于毫米波电路,FinFET晶体管的性能指标接近最后一代平面工艺,略有不如,但能量效率高一些;

3)单晶体管的性能只是毫米波电路设计中的一小部分,还有一些本文中没有写到的因素,比如电源电压和击穿电压、Self-Heating效应、DRC规则限制等等,这些方面平面工艺更有优势。

综合起来看的话,目前平面工艺还是能够得到更好的毫米波性能。

但是,最后一个但是,在芯片设计行业,性能不意味着最终就能胜出,往往是够用就行。

从CMOS和III-V族工艺的发展经历就成看出这一点。

在一个处处讲成本和收益之间trade-off的工程世界,完美主义是没有生存空间的。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2063期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

AI|台积电|

华为

|封测

|晶圆|

SIC

|

存储

|IC

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie