台积电5nm的更多细节披露

2020-03-23

14:00:07

来源: 半导体行业观察

来源:内容由半导体行业观察(icbank)

编译自「

wikichip

」,

谢谢。

在过去的十年中,台积电的运作节奏相当稳定。该公司于2019年

3

月开始生产其最新节点

5

纳米的风险产品。只要

COVID-19

不会中断运营,预计

5

纳米将在第二季度(可能在

4

月或

5

月)左右逐渐增加。本文从包括

Arm Techcon 2019

、第

65

届

IEEE IEDM

会议和

ISSCC 2020

在内的许多地方获取其信息。但让我们也有些失望的是,尽管该论文具有重要意义,但台积电的

IEDM

论文缺乏实质性内容,这并不符合我们对

IEDM

会议质量的期望。

台积电尚未透露

N5

节点的确切设备尺寸,因此我们将坚持自己的估计。我们目前的估计仍然是

48 nm

的多晶硅节距(

poly pitch

)和

30 nm

的金属节距(

metal pitch

)。这些尺寸得出的器件密度估计为

171.3 MTr /mm

²。而根据台积电在

IEDM

上的报告,

5nm

的密度比该公司自己的

N7

节点提高了

1.84

倍,但根据我们的估算,这个数字为

1.87

倍,两者相当接近。自台积电(

TSMC

)逐步扩展其

7

纳米节点以来,正好在

4

月份就标志着这一增长。令人印象深刻的是,这距离该公司在

1

6

nm

推出其首款

FinFET

器件还不到

5

年。从

N16

到

N5

,台积电目前正以摩尔定律

2x / 2

年的速度推出生产节点,这实际上快于历史趋势线。

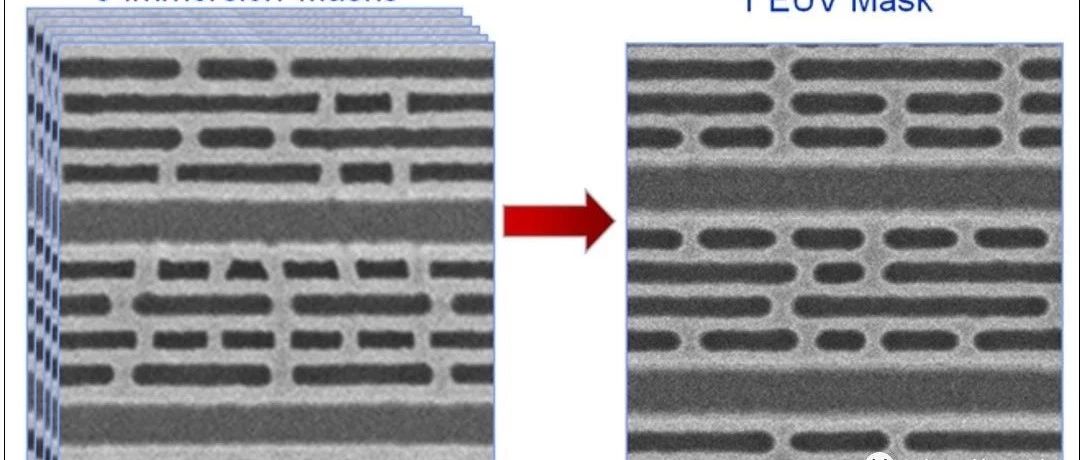

在

IEDM

论文的其中一张图中,

TSMC

展示了图案化

EUV

的保真度(

patterning fidelity

)。很难说我们能在多大程度上依靠他们在

IEDM

的介绍,但是如果我们假设此处的最小金属间距约为

30 nm

,则单元高度约为

〜

6T

(与

N7

相同),这是可行的达到约

180 nm

的

cell

高度,高密度的

cell

很可能是

2 + 2 yielding

的

8 F

in

C

ell

,但是如果

COAG

表示单鳍隔离,则

N5

可能是

7

Fin

的高度。换句话说,鳍间距(

fin pitch

)可能为

25-26 nm

。台积电确实提到有一个使用

3

F

in

的

HPC

C

ell

。如果我们假设

25 nm FP

,则

HPC

C

ell

的高度为

225 nm

或

7.5T

(也与

N7

相同)。

总体而言,台积电N5是一种高密度,高性能

FinFET

工艺,专为移动

SoC

和

HPC

应用而设计。

Fab 18

在台湾南部科学园区的公司新的

12

英寸

GigaFab

工厂中,

Fab

广泛使用了

EUV

工艺。台积电表示,其

5

纳米工艺比其

7

纳米节点的密度高

1.84

倍。台积电还优化了模拟器件,实现了大约

1.2

倍的扩展。在

IEDM

上,

Geoffrey Yeap

报告说,对于由

60

%逻辑,

30

%

SRAM

和

10

%模拟

/ IO

组成的典型移动

SoC

,他们预计将采用

5 nm

技术,能够将

die

的尺寸减少

35

%到

40

%。

从设备功率和性能的角度来看,TSMC表示,在等功率情况下,设备的速度提高了

15

%,或者在相同速度下,其功耗降低了

30

%。这些数字与先前报告的一致。

N7

随附的超

LVT

(

uLVT

)之外,还有一个新的极限

LVT

(

eLVT

),这可以将速度提高

15

%到

25

%。此外,与标准

N5

C

ell

相比,我们上面提到的

HP

C

ell

变体可以以密度代价,将性能再提高

10

%。

台积电强调在此过程中广泛使用EUV。值得指出的是,这实际上是台积电第一个基于“主要”

EUV

的节点。台积电

N7

和

N7P

节点是基于

DUV

的。台积电的第一个生产

EUV

流程是

N7 +

,但该节点实际上是一个孤立节点,与先前的节点不兼容,除了返回该节点之外,没有明确的迁移路径。另一方面,对于大多数客户而言,

N5

被设计为从

N7

迁移的主要途径。台积电表示,在切割,接触,过孔和金属线步骤中,使用了

10

层以上的

EUV

层来替代至少

4

倍的浸没层。这是将其基于

EUV

的

N5

节点与利用多重模式的假设

N5

节点进行比较得出的结果。

台积电在IEDM上展示了一张图表,报告说,与以前的工艺相比,

N5

首次使用更少的掩模。与基线的

1

倍

N16

相比,测量出图中条形的高度,

N10

使用的

mask

增加了

1.31

倍,

N7

使用的

mask

增加了

1.45

倍,而

N5

使用的

mask

增加了

1.35

倍。如果

N5

是基于多图案

DUV

的工艺,则掩模数量将激增至

1.91

倍。换句话说,在使用约

60

个掩模的

14 / 16nm

时,

10 nm

约需要

78

个掩模,

7 nm

约需要

87

个掩模,而

5 nm

则返回到

81

个掩模。如果没有

EUV

,则在

5nm

的时候需要

115

个掩模。他们没有给出与

N7 +

的比较,但我们估计它与

10 nm

的掩模数量相当。

为了改善驱动电流,台积电为其5纳米

FinFET

器件引入了高迁移率通道(

HMC

)。台积电(

TSMC

)尽一切努力避免详细说明该通道的实际属性(每个相关的问题都被重言式所使用:“那些知道,知道”的人)。但试图隐藏这样的通用信息是徒劳的,我们希望

TechInsights

在产品开始发货后的几个月内发布该信息。我们相信台积电正在为

pMOS

器件采用

SiGe

通道。据我们所知,这大约由

37

%的

Ge

组成。台积电表示,与同等的

Si finFET

相比,

HMC

的性能提高了

18

%。下面显示了全应变

HMC

晶格的

TEM

。

台积电表示,它已在其

N5

工艺中加入了许多定标助推器。有趣的是,台积电称它们为“智能超扩展功能”(

smart hyper scaling features

),这是英特尔以前使用的营销术语。台积电称之为

“唯一扩散终止”(“

unique diffusion termination

)的第一个助推器。我们认为,这是指

cell

边界处某种形式的单个扩散破坏。此外,

TSMC

还增加了在有源区(

COAG

)上降低栅极接触的能力。而英特尔先前在其

10

纳米节点上引入了这两项功能,并将其作为“超扩展功能”的一部分。

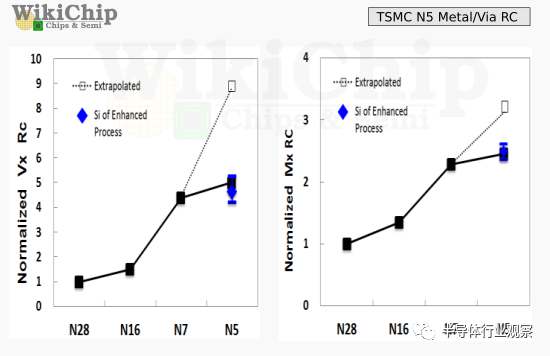

台积电(TSMC)表示,尽管间距趋于严峻,但金属线

RC

和通孔电阻与

N7

保持相对相似。台积电表示,这是通过“使用

EUV

图案,创新的按比例缩放的势垒

/

衬垫,

ESL / ELK

电介质和铜

reflow

来实现的。” 改进意味着互连

RC

相对于

N7

不会像

N7

相对于

N16

那样恶化。

台积电公布了两个

6T SRAM

变体:一个高性能单元和一个高密度单元。高性能

C

ell

为

0.025 µm

²,而高密度

Cell

为

0.021 µm

²。在绝对占位面积和它们各自类别中,这两个单元都是迄今为止最密集的

SRAM

单元。换句话说,即使是高性能

SRAM

单元,其密度也比迄今为止报道的所有其他正在生产的

SRAM cell

都要高。

以前,我们假设辅助电路的占比约为

30

%,这估计约有

32 Mib /mm

²的缓存。与

N7

的

24.7 Mib /mm

²相比,增加了

30

%。在

ISSCC 2020

上,台积电展示了带有

135 Mib HD SRAM

和附加

IP

的测试装置。他们报告的

H

D C

ell

密度确实与我们的估计相符。显示了

HD SRAM

阵列的

Shmoo

图,其中将其用作高性能

L1

高速缓存。他们能够在

0.85 V

的电压下达到

4.1 GHz

。仔细观察该图可以发现,如果将电压提高至

0.9 V

,则可以超过

4.2 GHz

。

在最近的两个节点中,TSMC的执行非常出色。自从其

16 nm

节点以来,每个过程节点的扩展速度都比其前身更快。

N7

是该公司最快的斜坡节点,有史以来最快的缺陷密度降低。台积电表示,它希望其

N5

节点的速度更快。

5

纳米工艺于

2019

年

3

月进入风险生产。该工艺有望在今年第二季度(可能在

4

月或

5

月)加速进行。如果增加速度,这将是晶体管密度和

SRAM

密度方面最密集的节点——超越三星和英特尔。三星

5

纳米仅比其

7

纳米稍密集,与台积电的

5

纳米相比没有竞争力。三星的下一个飞跃是其

3

纳米节点。英特尔很可能会凭借其

7

纳米节点获得密度领先优势,但是,该节点要到明年下半年才会推出

-

落后

1.5

年。

台积电(TSMC)

5

纳米节点将在

Fab 18

上投入生产,新的

12

英寸

EUV GigaFab

将分三期建设。第一阶段于

2018

年初完成,这是

5

纳米工艺的开始。第二阶段在稍晚些时候开始,预计也将在

2020

年投入量产。第三阶段的最后阶段于

2019

年开始,计划于

2021

年投入量产。

Fab18

还将成为其

3

纳米工艺的未来工厂,该工艺计划于

2022

年进行。

除了制程技术本身,台积电还在封装方面开展工作。CoWoS是公司当前的主要

2.5D

技术。台积电最近宣布推出

2

倍标线(

reticle

)

CoWoS

,其

HBM

带宽高达

2.7 TB / s

,特别针对

5

纳米节点进行了优化。将来,它将扩展到

3x

光罩和最多

8

个

HBM

堆栈。台积电还宣布了

SoIC

封装,这是该公司的

3D

堆叠封装技术。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2257期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

东南亚芯片

|传感器

|IGBT

|

SiC

|MLCC

|中兴|腾讯|半导体股价|芯片测试

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie