CMOS将成为历史?初创公司推出新型晶体管

2020-06-09

14:00:25

来源: 半导体行业观察

来源:内容来自

半导体行业观察综合

,谢谢。

据EEtimes India报道,英国初创公司Search For Next(SFN)计划推出一个叫做Bizen的晶体管,以取代在市场上使用了长达数十年的CMOS晶体管。而他们推出的这个方案设计也获得了英国政府170万英镑的激励。这笔奖金将会用于新工艺的进一步发展。

SFN的首席执行官David Summerland表示:“我们非常高兴看到英国政府认识到Bizen(晶体管)在使英国实现其雄心勃勃的净零排放目标方面将发挥的关键作用。” “ Bizen [使]英国能够在半导体制造领域发展领导地位。CMOS将成为历史。”

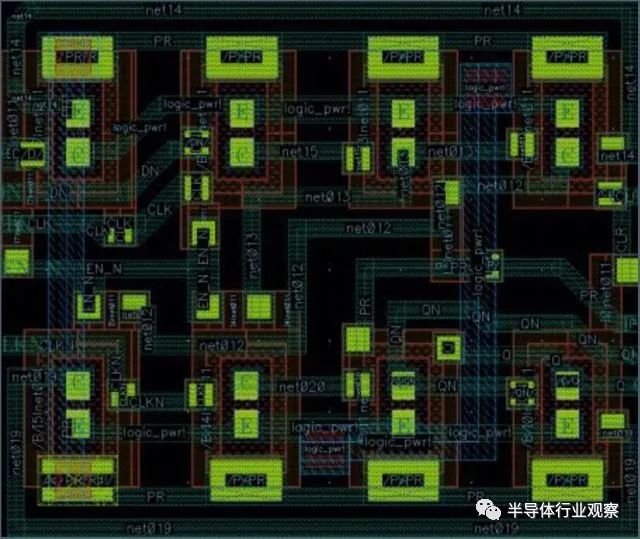

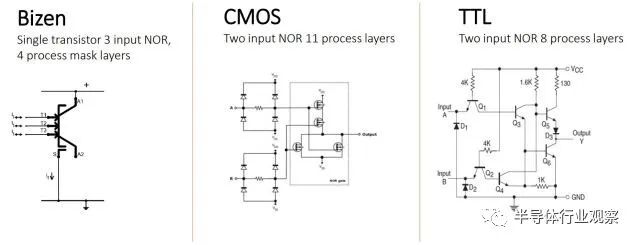

报道指出,Bizen晶体管设计是将双极结(bipolar junction )与齐纳二极管( Zener diode,)的概念结合在一起,利用量子隧穿效应消除了传统双极晶体管的电阻以及所有金属层。晶体管的栅极使用量子隧道连接;实际上,可以建立多个栅极连接,这意味着可以在一个晶体管内创建多个NOR和OR门,从而缩小了逻辑电路的管芯。

Summerland之前在接受EE Times的采访中 表示,尽管存在一些静态功耗要求,但Bizen晶体管可以达到或超过CMOS工艺技术的开关速度和动态功耗。Bizen还没有遭受CMOS静电放电(ESD)敏感性和闩锁问题(latch-up)的困扰。Bizen晶体管适用于数字晶体管和功率器件。

传统上,双极技术一直受到其对电阻器的需求的限制,电阻器的缺点是使用低功率器件会导致尺寸变大。相比之下,Bizen晶体管使用量子隧道技术,使设计人员能够像MOS器件一样消除电阻,并利用现在可控制的电流。这样就可以实现一个非常低功率的电路,其中的晶体管处于常开状态,但不饱和,并且由隔离的隧道连接控制,而不是像传统的双极型晶体管那样直接通过金属与基极的接触来控制。

因此,Bizen技术使设计人员可以创建更少层,增加逻辑密度的更简单的电路。例如,对于支持低至高电压操作的设备,Bizen器件所需的层数范围为4到8,而CMOS则为10到17。功耗降低,尺寸减小,集成度和速度提高,从而允许在英国现有的大型工厂中制造复杂的设备。

据该公司之前的新闻稿透露,与CMOS相比,Bizen的交货时间缩短了五倍,从15周减少到仅三周。此外,新工艺使栅极密度增加了三倍,从而使芯片尺寸相应减小了三倍。最后,Bizen将所需的处理层数减半。所有这些都是在达到或等于或提高当前CMOS器件提供的速度和低功耗功能的同时实现的。

SFN首席执行官David Summerland解释说:“由于几何尺寸的缩小违反了物理定律,CMOS加工行业正在遭受重创。我们回到最开始的地方,找到了一种将硅或宽带隙器件制造中的量子隧道力学商业化的方法。结果就是“ Bizen”(双极/齐纳),它保留了传统双极工艺的优点,但通过使用齐纳量子隧道力学消除了缺点。这可以带来较低的动态功率,较高的速度和较高的栅极密度,所需的处理层数减半,材料使用量减少了三分之二,并缩短了制造时间。这使任何晶圆厂都能成为类别杀手。”

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2335期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

两会|台积电|

RISC-V

|汽车芯片

|

AI

|EDA

|中美|晶圆|射频|

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie