CCF测试容错领域的技术盛会CTC2020来啦

2020-08-19

12:04:50

来源: 互联网

点击

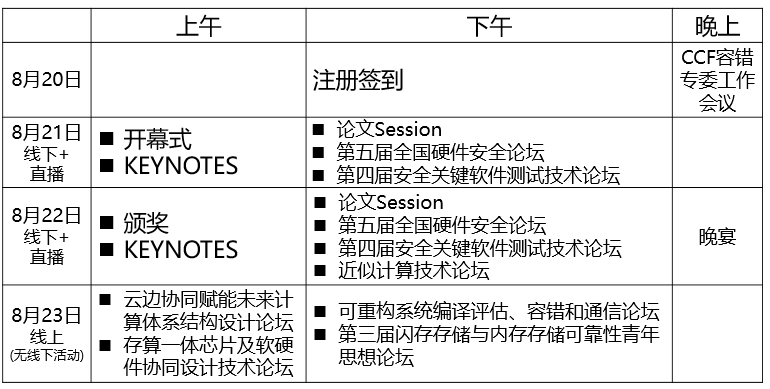

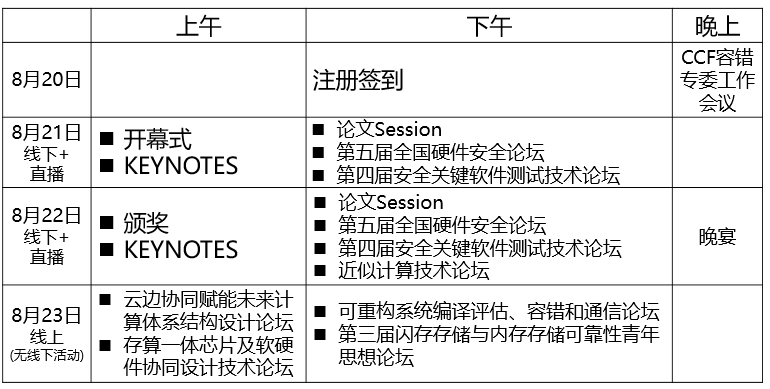

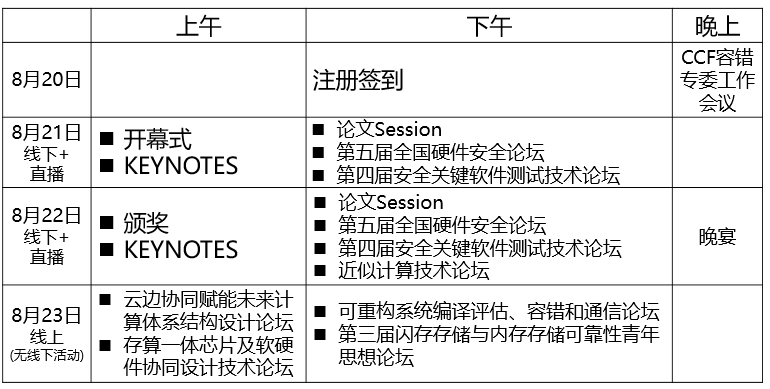

CCF容错专委年会——中国测试学术会议(CTC2020)将于8月20-23日在西安陕西宾馆召开,诚邀您相聚西安,本次会议也支持线上参会。

会议嘉宾

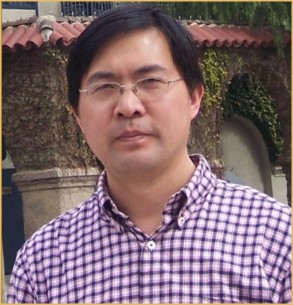

郝跃 院士 西安电子科技大学

郝跃院士长期从事新型宽禁带半导体材料和器件、微纳米半导体器件与高可靠集成电路等方面的科学研究与人才培养。在氮化镓/碳化硅第三代(宽禁带)半导体功能材料和微波器件、半导体短波长光电材料与器件研究和推广、微纳米CMOS器件可靠性与失效机理研究等方面取得了系统的创新成果。

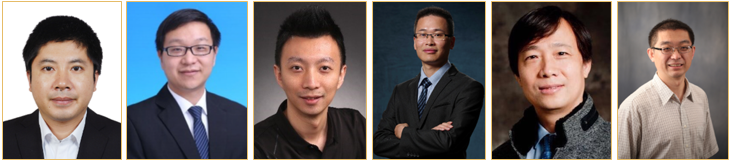

章迅 可靠性首席科学家

李必信 教授

刘杨 教授

Kris Gaj Professor

从事芯片设计自动化(EDA),新工艺(ReRAM 等)及算法(深度学习等)与计算机体系结构的协同优化,基于机器学习算法的芯片及硬件系统性能、可靠性提升等。在 EDA 与体系结构领域顶级/主流国 际会议和期刊上发表论文 50 余篇。其中一篇获 ICCAD 最佳论文提名。据 IEEE 数字图书馆统计,5 篇论文在其会议所收录的所有论文中引用数排前 5%。成果得到业界专家高度认可与跟踪引用,包括郑南宁院士,William Dally 院士,Chengming Hu,及数名 ACM/IEEE fellow,部分成果被纳入IEEE P1838标准,与台积电,华为及阿里巴巴合作多项技术落地商用。

第四届安全关键软件测试技术论坛

论坛主席:

王真 上海电力大学

云边协同赋能未来计算体系结构设计论坛

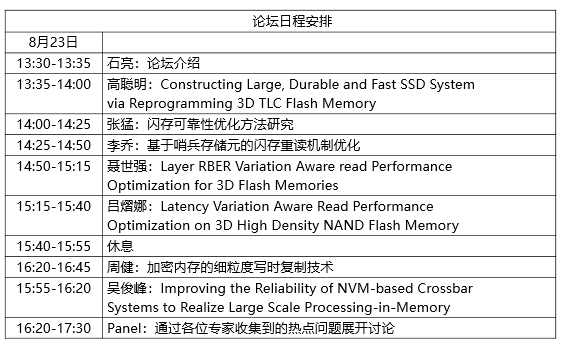

会议议程

会议嘉宾

大会主席:郝跃 西安电子科技大学 院士

组织主席:

刘有耀 西安邮电大学

董 军 西安邮电大学

于振华 西安科技大学

论坛主席:

左德承 哈尔滨工业大学

蒋 力 上海交通大学

石 亮 华东师范大学

潘 娅 西南科技大学

程序主席:

杜慧敏 西安邮电大学

黄 松 陆军工程大学

江建慧 同济大学

宣传主席:

邓军勇 西安邮电大学

朱 筠 西安邮电大学

杨博文 西安邮电大学

媒体主席:

陈卓俊 湖南大学

崔晓通 重庆邮电大学

识别二维码进入会议官网及注册通道

https://conf.ccf.org.cn/CCFCTC2020

大会特邀报告

郝跃 院士 西安电子科技大学

中国科学院院士,微电子学专家,微电子学与固体电子学博士生导师。安徽省阜阳人,1958年3月生于重庆市,1982年毕业于西安电子科技大学半导体物理与器件专业,1991年在西安交通大学计算数学专业获博士学位。九三学社第十四届中央委员会常委和九三学社陕西省委主委、中国电子学会副理事长、国际IEEE学会高级会员。

郝跃院士是国家中长期科学和技术发展规划纲要(2006-2020年)"核心电子器件、高端通用芯片和基础软件产品"科技重大专项实施专家组组长,国务院第七届学科评议组(电子科学与技术一级学科)召集人,国家自然科学基金委员会信息科学部主任,高等院校电子信息类专业教学指导委员会主任,教育部科技委委员,国家重大基础研究计划(973计划)项目首席科学家,陕西省科学技术协会副主席,微电子技术领域的著名专家。他是第九、第十、第十三届全国政协委员和第十一届全国人大代表。2013年11月当选中国科学院院士。

郝跃院士长期从事新型宽禁带半导体材料和器件、微纳米半导体器件与高可靠集成电路等方面的科学研究与人才培养。在氮化镓/碳化硅第三代(宽禁带)半导体功能材料和微波器件、半导体短波长光电材料与器件研究和推广、微纳米CMOS器件可靠性与失效机理研究等方面取得了系统的创新成果。

章迅 可靠性首席科学家

华为技术有限公司

ICT可靠性技术发展与挑战

华为技术有限公司经过三十多年的发展,已经形成一套较完善的可靠性技术体系和工程方法。报告内容涵盖公司可靠性业务发展与可靠性技术体系建设,同时介绍公司在软件可靠性、AI可靠性、复杂系统可靠性、功能安全等领域的探索与当前面临的挑战。

章迅,现任华为技术有限公司可靠性首席科学家、RAMS技术实验室主任、DFX技术委员会主任与RAMS首席技术专家,负责构建公司持续领先的可靠性、可服务性、节能减排、可制造性、可供应性等DFX技术能力。1998年西安理工大学研究生毕业加入华为技术有限公司,1998-2018年从事环境与可靠性实验、可靠性测试、系统可靠性设计、可靠性架构等工作,负责交换机、核心网等近十款重要产品的可靠性设计工作,建立公司可靠性组织、流程、技术、规范、工具等工程能力,主导负责了两个IEC TC56可靠性标准并发布,获得华为技术有限公司“蓝血十杰”称号。曾担任公司可靠性部部长、公司可靠性管理委员会主任及首席系统可靠性技术专家。

张承义 副总经理

天津飞腾信息技术有限公司

CPU芯片可测性设计技术与实践

硅后验证是的可控制性和可观察性严重不足,导致故障定位非常困难集成电路在完成流片后与实现量产前的重要步骤,是发现硅片深层次功能、性能故障的最重要手段。然而,相比硅前验证,硅后芯片的可控制性和可观察性严重不足,导致故障定位非常困难。报告对飞腾公司CPU产品在可测性设计方面的技术积累与实践经验进行介绍。飞腾CPU通过加强芯片设计阶段的硅后调试设计,实现了对微处理器类芯片的可控制性和可观察性的有效增强,辅以科学合理的调试流程,达到快速定位复杂故障的硅后调试水平。

张承义,博士,研究员,天津飞腾信息技术有限公司副总经理。长期从事国产高性能CPU研究与设计工作,先后参加多项高性能计算机和高性能CPU核高基重大专项课题、863重大项目、基金和预研项目,参与多款国产飞腾系列CPU研制和应用推广。获得国家科技进步特等奖1项、一等奖1项,省部级科技进步一等奖2项,在国内外重要刊物或会议发表论文30余篇,申请专利20余项。

李必信 教授

东南大学软件工程研究所所长

结合团队的研究兴趣和研究成果,围绕软件全生命周期的多种缺陷检测技术展开系统的介绍。内容涵盖软件全方位缺陷检测技术的原理方法、发展轨迹和核心关注点。

李必信,1969年8月出生,2001获得南京大学博士学位,2001-2003分别在芬兰、挪威和荷兰等地博士后出站。 现任东南大学计算机科学与工程学院教授、博士生导师,东南大学软件工程研究所所长。

2006年入选教育部新世纪人才培养计划、2011年度中创软件人才奖获得者、2014年获得教育部科学技术奖(自然科学奖)二等奖(排名第一)。

中国计算机学会软件工程专委会委员、容错计算机专委会常务委员,江苏省软件工程标准化委员会主任委员,江苏省计算机学会软件专委副主任。

研究方向为软件建模、分析、测试与验证、智能软件架构理论和方法、软件演化和软件质量保证等。从1999年开始,主持各类基金项目40多项, 先后在"IEEE Transactions on Network and Service Management", "ACM Computing Surveys","Information and Software Technology", "Software Testing, Verification and Reliability","Journal of Systems and Software","Advance in Engineering Software", "International Journal of Software Engineering and Knowledge Engineering", "Journal of Computer Science and Technology", 《软件学报》、《计算机学报》、《计算机研究与发展》国内外著名期刊和ICSE、FSE、ASE等重要国际会议发表学术论文180余篇,出版专著3部,教材1部,授权发明专利40项。论文被三大检索(SCI,EI,ISTP) 收录200多篇次,被他人引用累计超过5000篇次。

刘杨 教授

新加坡南洋理工大学

基于开源大数据的漏洞检测平台

软件漏洞一直是软件安全研究领域的一个痛点。不同的编程语言和不同的计算平台引入的不同类型的漏洞让这个问题变得更难了。同时开源平台的广泛使用,使漏洞的传播速度进一步加快。这个报告主要讲述我们如何在开源项目里面快速高效的识别开源版本,搜索已知漏洞。在开源项目的commit里面找到有漏洞的代码。然后利用找到的漏洞的标签数据,使用人工智能的算法来找未知漏洞。最后探讨一下我们在代码语义表征的一些尝试去更好的用图网络学习程序语义。整个工作已经形成一个完整的在线平台,支持全部的主流的开发语言的源码已知漏洞扫描(源码SCA扫描),支持C、C++, Java, APK的二进制和各种firmware已知漏洞扫描(二进制SCA扫描),支持APK的全方位漏洞扫描(SAST扫描)。

刘杨,新加坡南洋理工大学(NTU)计算机学院教授,NTU网络安全实验室主任、HP-NTU公司实验室项目主任以及新加坡国家卓越卫星中心副主任,并于2019年荣获大学领袖论坛讲席教授。刘杨博士分别于2005年,2010年分别获得新加坡国立大学学士和博士学位,2012年加入南洋理工大学。刘杨博士专攻软件验证,软件安全和软件工程,其研究填补了形式化方法和程序分析中理论和实际应用之间的空白,评估了软件的设计与实现以确保高安全性。到目前为止,他已经在顶级会议和顶级期刊上发表了超过300篇文章。他还获得多项著名奖项,包括MSRA fellowship,TRF Fellowship, 南洋助理教授,Tan Chin Tuan Fellowship,Nanyang Research Award 2019,NRF Investigatorship,并且在ASE、FSE、ICSE等顶级会议上获得10项最佳论文奖以及最具影响力软件奖。

Kris Gaj Professor

George Mason University U.S.A.

Post-Quantum Cryptography in Hardware and Embedded Systems:

Toward Choosing the Most Efficient and Flexible New Public Key Cryptography Standards

Post-Quantum Cryptography (PQC) refers to a new class of cryptographic algorithms that are resistant against all known attacks using quantum computers, but at the same time can be implemeted by themselves using traditional computing platforms, such as smartphones, tablets, laptops, and hardware accelerators based on integrated circuits. PQC is a cryptographic community's response to the emerging threat of full-scale quantum computers, expected to be developed within the next decade or two. The main goal of PQC is to replace the existing public-key cryptography standards, protecting the majority of the Internet traffic, such as RSA and Elliptic Curve Cryptography (ECC). The PQC standardization process, launched by the American National Institute of Standards and Technology in 2016, has recently reached Round 3, with 7 finalists and 8 alternate candidates remaining. These algorithms represent five major PQC families: code-based, isogeny-based, lattice-based, multivariate, and symmetric-based, and can be used to implement encryption, digital signature, and key exchange schemes of the future. Implementing PQC algorithms in hardware involves a unique set of challenges. Some of these challenges are specific to the current state of standardization, in which a large number of candidates remain. Others will persist for years after the first standards are published. This talk will summarize the current state of knowledge on the hardware efficiency of candidates for a new PQC standard and describe directions for future research and development in this new exciting area of science and engineering.

Kris Gaj is a professor in the ECE Department at George Mason University, U.S.A., located near Washington D.C. He is a co-director of the Cryptographic Engineering Research Group (CERG), involved in the majority of previous and current cryptographic competitions, from AES to PQC. In particular, his team has led hardware evaluation of candidates for the new hash function standard, SHA-3 in 2010-2012, and for the new authenticated cipher portfolio, CAESAR, in 2016-2019. His current research and teaching interests include cryptographic engineering and hardware security, with the special focus on the development of new hardware architectures and embedded system implementations for post-quantum public-key cryptosystems, lightweight cryptography, and codebreaking, as well as benchmarking of cryptographic hardware and embedded systems, high-level synthesis, software/hardware codesign, and side-channel analysis.

蒋力 上海交通大学副教授,博导

蒋力 上海交通大学副教授,博导

从事芯片设计自动化(EDA),新工艺(ReRAM 等)及算法(深度学习等)与计算机体系结构的协同优化,基于机器学习算法的芯片及硬件系统性能、可靠性提升等。在 EDA 与体系结构领域顶级/主流国 际会议和期刊上发表论文 50 余篇。其中一篇获 ICCAD 最佳论文提名。据 IEEE 数字图书馆统计,5 篇论文在其会议所收录的所有论文中引用数排前 5%。成果得到业界专家高度认可与跟踪引用,包括郑南宁院士,William Dally 院士,Chengming Hu,及数名 ACM/IEEE fellow,部分成果被纳入IEEE P1838标准,与台积电,华为及阿里巴巴合作多项技术落地商用。

论 坛

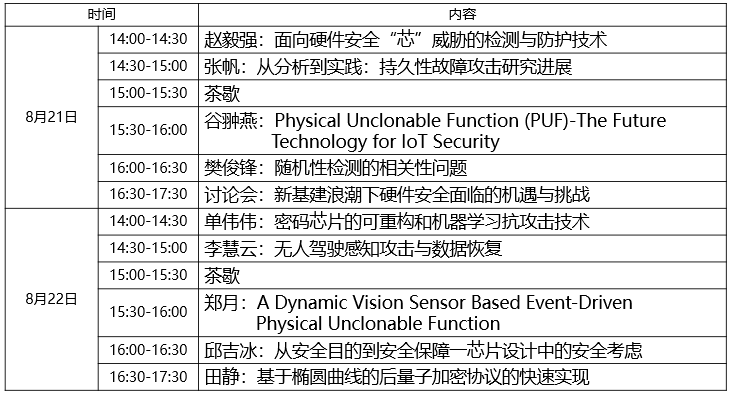

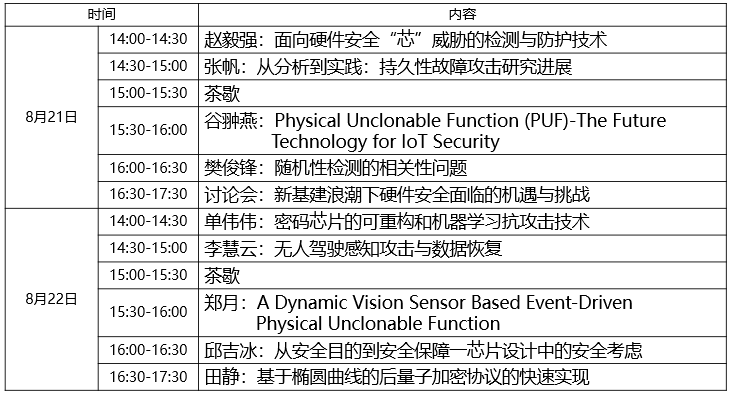

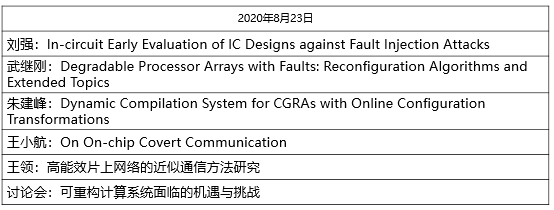

第五届全国硬件安全论坛

论坛共同主席:

胡伟 副教授,西北工业大学

胡伟 副教授,西北工业大学

曹元 教授,河海大学

讨论会主席:

张吉良 特聘研究员,湖南大学

张吉良 特聘研究员,湖南大学

来金梅 研究员,复旦大学

论坛指导委员会:叶靖 副研究员,中科院计算所

张吉良 特聘研究员,湖南大学

李晓维 研究员,中科院计算所

屈钢 教授,马里兰大学

集成电路设计供应链的不断全球化和计算设备的普遍互联使得硬件安全问题日益突出。现代计算机硬件通常处于交叉信任的计算环境并被不同安全级别的计算任务背靠背式共享;日趋丰富的互联特性则将关键硬件资源暴露给攻击者,使得攻击者无需物理接触硬件设备即可发起硬件攻击。近年来日益增多的硬件安全攻击表明:集成电路硬件已经成为发起跨层和远程攻击的有效切入点,亟需研究并解决好硬件安全问题。

全国硬件安全论坛迄今已成功举办四届,是集成电路硬件安全领域的重要学术研讨会,为国内外硬件安全领域的同仁提供了一个良好的学术与技术交流平台以及增进相互了解的沟通渠道。历届论坛邀请了国内外研究团队介绍硬件安全方面的最新研究成果并展望本领域的发展动态,积极促进了硬件安全相关领域的研究工作和交流合作,取得了积极的反响。

第五届全国硬件安全论坛将于2020年8月21日至22日在西安陕西宾馆举行。论坛有幸邀请到了来自国内外学术界和工业界的知名硬件安全专家9人。特邀嘉宾们将就芯片安全防护与威胁检测、无人驾驶感知安全、物理不可克隆函数、密码算法实现安全分析以及后量子密码等方面作精彩报告。我们期待与各位同仁相聚古城西安,共同领略和指点硬件安全领域的研究发展。

第四届安全关键软件测试技术论坛

论坛主席:

黄松 教授,中国人民解放军陆军工程大学

惠战伟 助理研究员,军事科学院

黄松 教授,中国人民解放军陆军工程大学

惠战伟 助理研究员,军事科学院

国内软件测试领域一直存在两个群体,一个是以高校为代表的学术研究水平见长的学术派,一个是以军方测评机构为代表的工程技术水平见长的实践派,安全关键软件测试技术论坛设置的初衷就是旨在分析军用及安全关键软件测试领域存在的共性技术需求和痛点问题,抽象出其中的理论问题开展学术研究,为学术界和企业界之间搭建一个高水平的交流平台。

2017年,由计算机学会容错专委副主任黄松教授发起,惠战伟博士具体实施下,在南京第17届全国容错计算学术会议上开设了首届安全关键软件测试技术论坛,得到了学术界和企业界的广泛响应,论坛参会人数超过100人,成为大会最有影响力的技术论坛。2018年,第二届论坛在哈尔滨举行,参会人数突破150人,同时吸引了国内从事软件测试产品自主研发的多家企业和军工单位的广泛参与,在业界取得了强烈反响。2019年,第三届论坛在北京九华山庄举行,参会人数突破200人,14场产学研各界大佬的报告高潮迭起,会场座无虚席,赢得各界一致好评。

本届论坛由中国计算机学会容错计算专委会主办,于8月21-22日在西安陕西宾馆举行,参会人数预计100人左右。会议同时将开启线上直播新模式,方便受疫情影响未能参加会议的同仁们线上讨论参会。

本届论坛将邀请11位关键软件测试测评技术研究机构的权威专家与工业界展开专题研讨,共同关注安全关键软件测试在自主可控和智能化方面面临的挑战、核心技术,以及当前的研究和应用热点。结合当前业界讨论的热点问题,论坛组织2个主题的Panel讨论。

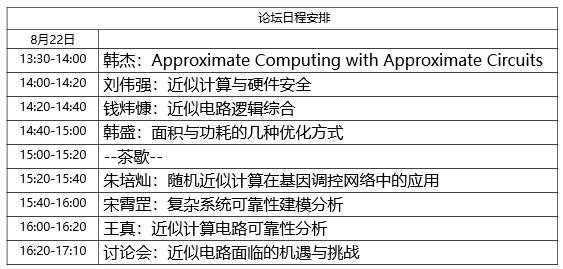

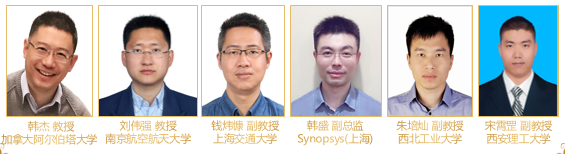

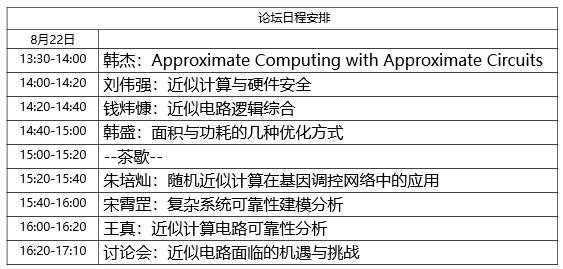

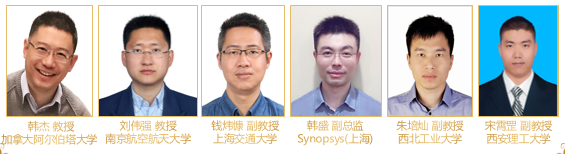

近似计算技术论坛

论坛主席:

王真 上海电力大学

论坛指导委员会:

韩银和 研究员,中科院计算所

韩银和 研究员,中科院计算所

江建慧 教授,同济大学

蒋力 副教授,上海交通大学

乔飞 副研究员,清华大学

未来的计算架构不仅需要支撑高通量计算力,也需要满足对低功耗的需求。许多新兴学科和应用共同依赖的平台可以是概率建模和随机计算,面向差错容忍应用,近似计算通过降低输出质量以获取应用的高性能,正是吻合了新形势需求下的计算模式。近似电路以低复杂度低功耗的设计,获取整个电路在面积、成本、性能上的收益,近年来引起了广泛关注。

近似计算技术论坛将于8月22日在西安陕西宾馆举行,一个崭新而极富生机的研讨平台即将呈现。论坛有幸邀请到了来自国内外学术界和工业界的知名近似计算领域专家,特邀嘉宾们将就近似计算与近似电路、近似计算中的硬件安全、近似电路逻辑综合算法、最新工艺下面积与功耗优化以及近似随机计算的应用等热点问题作精彩报告,并就近似电路的落地、可靠性等议题呈现思想火花的激烈碰撞!我们期待与各位同仁相聚古城西安,共同领略和指点近似计算领域的研究发展。

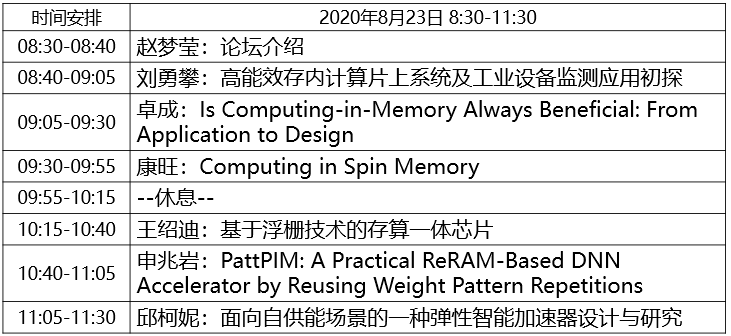

存算一体芯片及软硬件协同设计技术论坛

论坛主席:

赵梦莹 副教授,山东大学

赵梦莹 副教授,山东大学

冯诺依曼计算架构下,虽然运算单元算力和存储器性能都有显著提升,但两者差距越来越大,尤其是深度学习应用中数据搬运的时间和能耗可能远超计算的代价,使得“内存墙”的问题愈发显著。该背景下,存算一体的概念受到了学术界和工业界的广泛关注,如何发展存算一体技术是当代计算机发展的重要课题之一。

该论坛邀请了存算一体领域的知名学者,带来前沿的创新性报告,内容涵盖存算一体的架构设计、片上系统设计、以及结合神经网络和工业设备监测等不同领域的应用级解决方案,探索了基于不同存储介质(如自旋电子、浮栅技术、电阻式随机存储器等)的存算一体技术,为我们带来一场存算一体芯片及软硬件协同设计技术的饕餮盛宴。

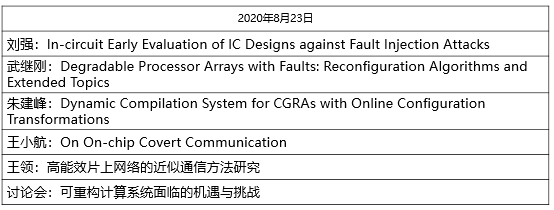

可重构系统编译评估、容错和通信论坛

论坛主席:

陈乃金 教授,安徽工程大学

陈乃金 教授,安徽工程大学

论坛指导委员会:

李华伟 研究员,中科院计算所

李华伟 研究员,中科院计算所

向 东 教授,清华大学,国家杰青

江建慧 教授,同济大学

刘雷波 教授,清华大学

徐江涛 教授,天津大学

可重构计算系统既具有专用集成电路的高计算速度及效率,又具有微处理器的可编程性和良好的灵活性。对于嵌入式系统等计算密集型任务方面的应用已经展示了巨大的优势。同时,可重构计算系统又不同于众核图形处理单元(graphic processing unit, GPU)。可重构计算结构实质上可以看成是由时间域和空间域构成的二维或三维结构,其在时间域的灵活性是通过运算操作节点任务在可重构阵列上的映射和调度实现的;空间域上是通过重复使用可重构的运算单元阵列,通过配置功能块来实现的,它是一个流水线结构。

可重构系统编译评估、容错和通信硬件安全论坛将于2020年8月23日线上举行。论坛有幸邀请到了知名可重构系统安全专家5人。特邀嘉宾们将就抗故障注入攻击的电路早期评估、带故障的可降解可重构处理器阵列算法与扩展、在线配置转换的粗粒度可重构计算动态编译、片共同探索可重构系统编译评估等领域的研究进展。

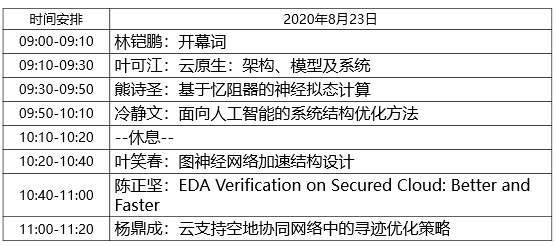

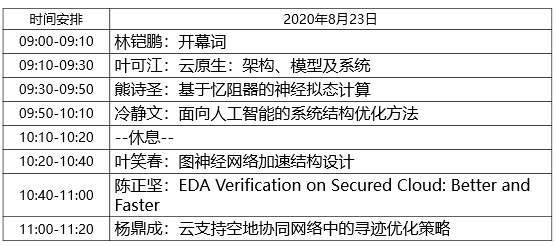

云边协同赋能未来计算体系结构设计论坛

论坛共同主席:

徐子晨 教授,南昌大学

徐子晨 教授,南昌大学

林铠鹏 国微思尔芯

云计算是当前大规模分布式计算的基础,边缘计算是可见的5G、物联网、物理信息系统等扩展式计算的集合,云边协同是必然产生新型计算模式的基本逻辑架构。一方面,计算系统设计、从EDA设计、芯片设计到物理信息系统优化乃至数据中心体系结构等越来越复杂;另一方面,云边协同使能体系结构设计与应用所需算力呈指数级提升,并达成特定场景内典型应用的可定制需求。因此,如何有效利用合理的设计与算法,充分挖掘现有及未来算力的潜能,赋能从材料生成、EDA工具设计、到新型计算体系结构设计等一体式的、具备全观性的探讨,是工业界与学术界共同关心的热点问题。本论坛拟邀请学术界、工业界同仁分享在相关领域内的不同研究及应用实践前沿工作,引发大家共同讨论解决上述问题的方法,找到可行的解决方案,为我国工业界可容错计算系统设计提供参考,做出贡献。

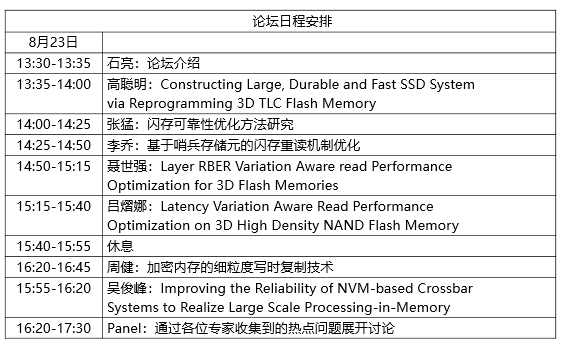

第三届闪存存储与内存存储可靠性青年思想论坛

论坛主席:

石亮 教授,华东师范大学

石亮 教授,华东师范大学

论坛秘书:

李昌龙 香港城市大学

李昌龙 香港城市大学

随着闪存,特别是3D闪存的快速发展,可靠性问题成为阻碍其快速部署和高效运用的关键问题。除此之外,包括DRAM和NVM也是目前存储发展的关键。本论坛中我们邀请到了多位青年博士后和博士生发表他们在此课题上面的观点,为青年人才提供交流和学习的机会。通过本次论坛的展开,我们将能够清晰的看到在闪存存储和内存存储可靠性方面关键问题和技术,为此领域的研究提供重要的基础。

Accurate Approximate Computing Circuit Reliability Analysis Methods

学术论文报告

测试理论与技术(集成电路验证与调试、测试仪与测试平台、软件测试、安全攸关缺陷的程序分析与验证、故障诊断)

容错计算(可靠性与安全性度量和评估、可靠性设计、国防,航天等行业容错系统设计应用、可信与安全芯片)

测试,容错,可信技术的应用

硬件安全(物理不可克隆函数、FPGA安全、硬件辅助软件安全)

领域定制加速器

电动汽车,无人汽车中的测试,可靠,可信,辅助设计技术

物联网测试,可靠性,安全,功耗等相关技术

物联网测试,可靠性,安全,功耗等相关技术

可重构设计,测试,容错,安全等相关技术

基于随机森林算法的集成电路适应性测试方法

片上网络的测试技术研究

应用直接编程接口技术提高片上系统的UVM验证重用性

基于遗传进化策略的处理器验证方案

ATE高速测试负载版的复用器和解复用器设计

关于无人自主系统试验鉴定的初步思考

基于模板挖掘的程序自动修复方法

基于软件度量的集成测试序列生成方法

一种层次化测试建模及测试用例设计方法

蜕变测试在机器学习领域的应用

基于故障预防的雷达嵌入式软件质量保证研究

X协议环境下GUI自动化测试原理分析及框架设计研究

基于场景分析的卫星运控系统软件测试方法

基于信号量的中断访问冲突规避方法设计与实现

一种基于对抗神经网络的软件缺陷挖掘方法

面向多位扫描单元的可诊断性设计方法

基于扩展日志的开源软件运行时故障诊断及实例研究

针对 RRAM 阵列 IR-Drop 效应对计算精度影响的快速仿真方法

ERMC:统一的高能效高可靠性 DNN 模型压缩框架

训练数据对抗攻击扰动对LeNet-5深度学习模型的鲁棒性影响分析

高轨卫星星载控制计算机可靠性分析

差错容忍的神经网络混合精度量化方法

WiNoC中基于数据包等待时间的无线token机制

基于交叉开关仲裁的流量自适应WiNoC设计

基于跳数的空间TTE 控制网络确定性动态调度算法

微体系结构缓存侧信道攻击与防御综述

防御StarBleed漏洞的FPGA配置位流混淆方法

基于PUF的硬件辅助软件认证方法

基于核函数编程的专用体系结构理论加速比研究

基于忆阻交叉阵列的时钟频率驱动递归神经网络电路设计

图数据压缩格式对广度优先搜索算法影响的特性化分析

基于强化学习的流应用动态自适应检查点机制

基于强化学习的流应用动态自适应检查点机制

基于异步检查点机制的细粒度流分区负载均衡方法

车载以太网测试体系研究与分析

基于改进再分配伪逆法的高速飞行器RCS控制分配设计

自供能存算一体系统中一种可配置DC-DC 转换器的特性研究

忆阻器的三值逻辑门和加法器设计

忆阻器的三值逻辑门和加法器设计

可重构阵列结构下基于混合粒度的SVDC算法并行化实现

Statistical Static Timing Analysis for Circuit Aging Prediction

A novel cross-project software defect prediction algorithm based on transfer learning

Mutation Testing for Integer-overflow in Ethereum Smart Contract

Sta-SFL: An Effective Framework on Locating Bugs For Mission Critical Software

Research on High Level of Hyper-heuristic Framework for MOTCP

LagNet: Laser-Guided Backdoored Neural Network

Minor sensor fault identification through kernel extreme learning machine based on extended state observer

Linear Active disturbance rejection control design for hypersonic vehicle with packet dropouts

The Non-inclusive Diagnosability of Multiprocessor System based on (n,k)-Star Networks

Integrating Two Logics into One Crossbar Array for Logic Gate Design

Bootstrap Based Resampling Methods for Software Reliability Measurement Under Small Sample Condition

A TSV repair method with the improved FNS-CAC codec

RAB: Recomputation Aided Backup for Energy Efficient Non-volatile Processors

A New External Active IC Metering Scheme to Resist IC Overbuilding

Design and certification of lightweight reconfiguration RO-PUF for FPGA

Energy-Efficient Physical Unclonable Function based on Ultra-low Standby Power Latch in 22nm FDSOI Technology

DIDO: A Dual-Input Dual-Output Router Architecture for On-Chip Networks

An anti-interference low-power double-edge triggered flip-flop based on C-elements

L1-Norm Group Normalization: An Energy- Efficient and Stable Normalization Method of Deep Neural Networks

Fault Detection Method for Wi-Fi Based Smart Home Devices

Efficient Scheduling Mapping Algorithm for Row Parallel Coarse Grained Reconfigurable Architecture

Fault-Tolerant Control Allocation System for Hypersonic Vehicle RCS under Multiple Faults

Fault-Tolerant Control Allocation System for Hypersonic Vehicle RCS under Multiple Faults

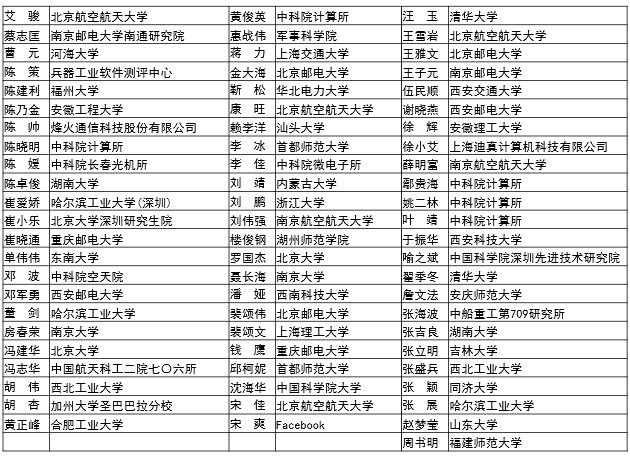

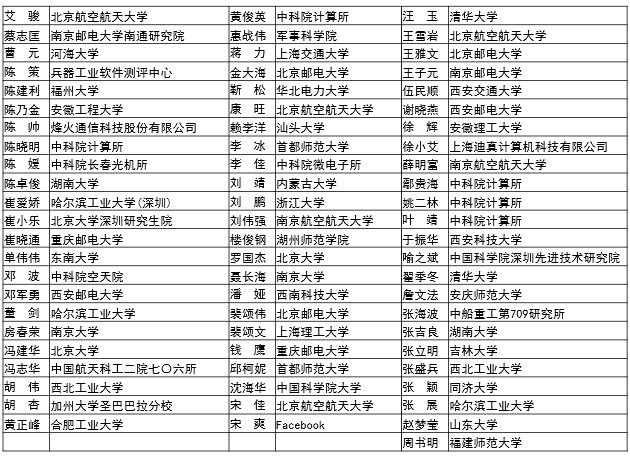

程序委员会

责任编辑:EricZhou