EDA向左,芯片向右

来源:内容来自公众号「ICGeek」,作者:Alice Gao,谢谢。

我叫小E,来自银河系中的EDA部落,我们的部落诞生于1981年,部落的前身名为CAD,更准确的说是VLSI-CAD。我最好的朋友,小芯,来自芯片联盟,1947年在贝尔实验室,科学家肖克利发明了晶体管,成为联盟第一公民,这是一项改变世界的发明,开启了以联盟为基石的人类文明的信息技术时代。部落自诞生以来便效忠联盟,以自动化的设计流程使得更大规模的芯片设计成为可能,从而成为联盟发展最重要的引擎。

由银河系历代的算法,架构,工艺特工为小E和小芯加持新技能,这使我们持续变得更加强大,经历了从科技大爆炸到更加辉煌的数字时代。这个时代源于一项伟大的技术,叫做5G,5G有多伟大?这么说吧,当今世界最为重要的一场战争,战场就从5G打响,初期人们有意无意间已经把中美贸易战等同于5G竞争。

在这个时代会有哪些新的变化,小E和小芯的未来又该何去何从?接下来,给大家讲讲我们的故事,故事的名字叫做: EDA向左,芯片向右。

这个故事的前传也推荐大家看一看(入口在文末推荐阅读)

一芯一E,我们的征途是星辰大海

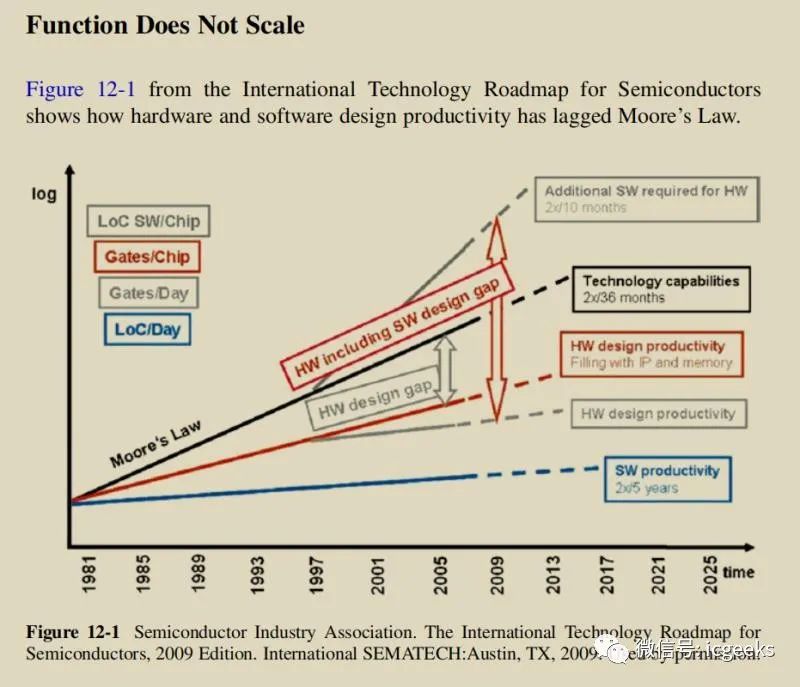

5G开启了以ABCDI A(AI)B(Block Chain)C (Cloud Computing) D (Data) I(IoT)为特征的智慧时代,这给联盟带来两个重要的变化: 一是传统计算向智能计算转型 ,摩尔定律无法支撑一块钱能买到的算力持续暴涨的需求,从系统角度看成本,面积,执行时间,功耗等通常会产生冲突,设计方法需要从系统视角靠算法和算力打通软件与硬件的任督二脉, 二是嵌入式在智能家居,智能汽车,物联网领域的崛起 ,更严苛的场景要求和计算,频率,功耗约束给设计提出新的期望和挑战。

过去芯片设计直接把PPA的指标当目标,一切以满足PPA为准。但是到了5G时代,随着小爱同学的加盟,目标就变成了从系统看一个元能买到的算力,架构演化和hw-sw codesign都是被这个内在动力驱动的。然后新的铁三角就不是PPA了,而是, 1. 一个元能买到的算力(ROI),2. 质量,3,约束 (PPA,时间,成本)

需要权衡的因素更多,问题的复杂性加深。市场说SPEC不容易给,验证说希望芯片能够早期验证,时间和成本都是问题,软件说,希望能早些开始工作而不是流片后,PR说,希望前端交付的代码后期可以被实现。面对这些需求,挑战和转型,我们已做好充分的准备,开启了设计流程开始从过去的串行依赖转向渐进明细的探索之旅。

在技术上,EDA持续投资系统开发的领域,引导软硬协同设计的方法学,并为之提供不同的验证能力,从IP和工具角度,建模方式更加成熟,提供模型,不同环节的模型之间紧密连接和整合,逐步丰富早期阶段的模型参数,IP建模,准确性,功能指标,性能参数,功耗建模,完整性大大提升,同时,自动化能力持续快速提升。

在工程协作中,不同岗位角色加大融合,软硬,验证与设计,前端与后端,设计与工艺,他们之间你中有我,我中有你,彼此依赖嵌套,越来越紧密的整合在一起,并且能够在同一个团队中更好的协同。

有了这些强大的动力引擎,勇敢的IC特工们继续向星辰大海出发,请大家跟随宇航员小E,一同开启我们的芯际之旅,倒数10秒

10!9!8!7!6!5!4!3!2!1!出发!

软硬协同,天下大同

旅行的第一站,软硬协同芯球。

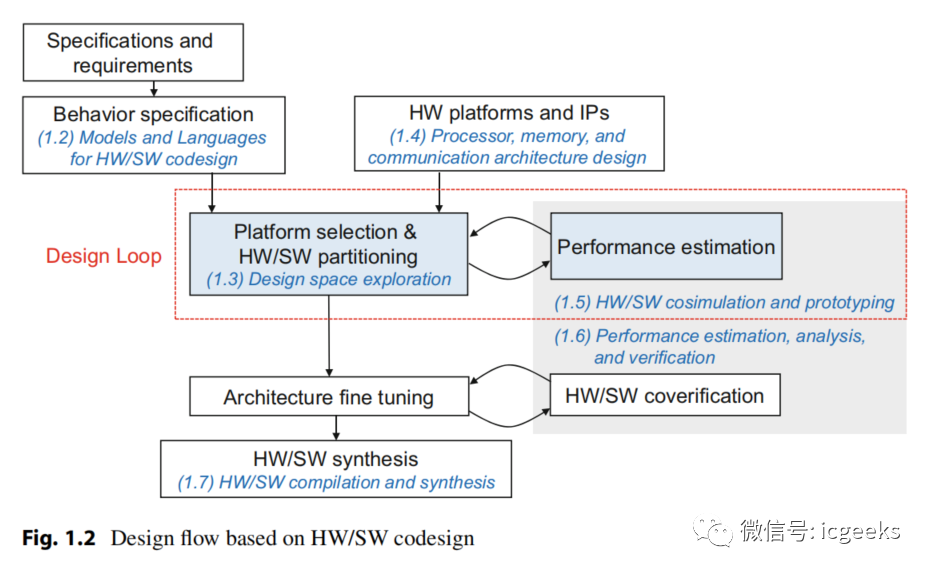

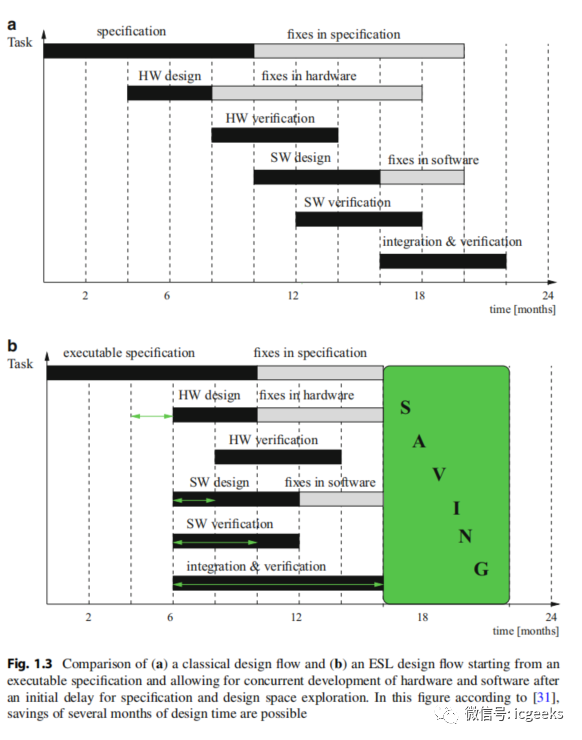

软硬协同的方法学兴起于1990年代初,目标是对系统行为在高层建模,设计早期系统空间探索,估算系统性能和资源需求,减少设计时间和成本,曾经是Intel, Nvidia等公司的主流方法,随着EDA技术成熟和5G相关的市场崛起,它已经逐步成为复杂电子系统以及分布式嵌入式系统的标准流程。

相关的技术演化我们通过如下对比会获得一些更直观的感受:

流程1:

-

有了spec收集直接进入算法选择阶段

-

手工决定硬件架构和如何做软硬划分

-

切分后进入硬件设计阶段,之后是软件设计阶段

-

软件交付后进入系统测试和调试阶段

-

如有问题,回到step2,重复步骤2,3,4,5,直到清除所有问题和阻碍

-

进入实现阶段

流程2:

-

有了初始的需求和spec先进入spec建模,工具支持系统空间探索,辅助决策软硬切分策略

-

基于虚拟原型和软硬协同仿真技术进行早期性能评估以获得合理的软硬切分策略

-

协同验证以确定架构设计的合理性

-

软硬协同编译及高阶综合

基于流程1所花费的时间为22个月,基于流程2,所花费的时间为16个月,通过这种协同的方式可以使得系统设计周期时间节约6个月。大家有没有感受到技术进步的力量呢?

IP,部落的黄金,联盟的基石

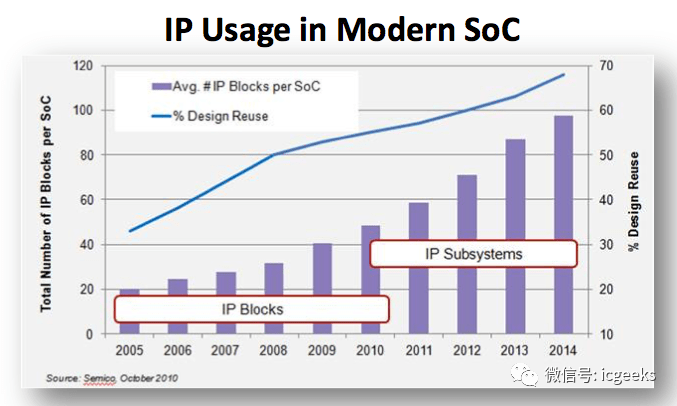

我们紧接着进入IP的世界,过去几十年,随着芯片集成度和复杂性不断提升,Designer常常要在一个芯片中集成进上百个IP,一套切实可行的IP集成,复用,开发的方法对SOC设计至关重要。IP对于SOC设计有多重要呢?这么说吧, 现代SOC设计的比拼就是拼IP,拼集成方案。

两大EDA厂商早在九十年代就开始注重在这个市场的投入,且早已成为EDA巨大的增量市场,是部落的黄金,据2020Q1最新数据显示,Synopsys已经超越ARM成为全球第一大IP供应商,Cadence紧随ARM之后,屈居第三,而ARM也与这两大EDA巨头有密切的合作,为系统和芯片厂商提供一体化解决方案。

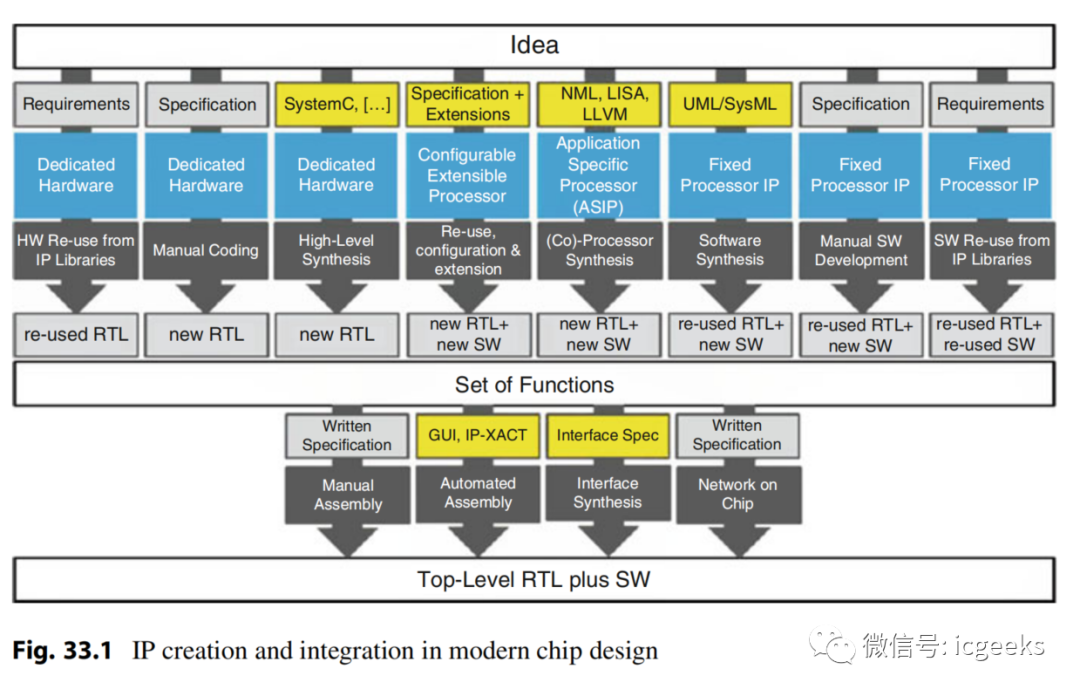

在传统的解决方案中,IP被集成进SOC的姿势是这样的:

1. 手工被集成进SOC

2. HLS

3. 利用可扩展或可配置的处理器内核

4. 利用工具基于ASIP (Application-Specific Instruction-set Processor)创建

5. 从系统模型自动生成软件

6. 基于标准处理器手写软件

EDA在IP领域可以依靠生态影响力把行业的IP(标准,规范,协议)通用需求固化和领域需求差异化,为专用领域,如汽车电子,AI等提供打包的一揽子解决方案,满足该领域的行业标准及合规性。 这些更底层的问题交给专业的供应商,自动化可配置的工具链可以有效支持自动生成SOC集成方案,支持SOC架构师更加聚焦架构级的探索。

SOC集成IP,需要包含在硬件和软件中的新功能,协调IP重用和IP开发之间的矛盾以更有效的应对复杂性。在有了软硬协同设计的方法学和更加成熟的IP建模方案之后,对于IP开发,有六种基本方法来实施一个全新的理念:

1. Software Development Kits (SDKs),硬件细节建模不完整

2. 虚拟平台建模,寄存器行为及硬件功能准确,缺乏timing信息,或使用cycle accuracy的建模方式,在speed vs. accuracy之间达到一个平衡

3. Emulation

4. RTL simulation

5. FPGA原型为软件开发提供环境

6. 实体芯片为软件开发提供环境

验证成本是SOC开发成本的大头,IP级的验证在其中做的可深可浅,采购安全及质量合规的,超大规模量产验证过的,PPAC最优的IP及相应的VIP显得尤为重要,验证IP的巨额成本由供应商承担,SOC厂商也愿意为此买单并分摊成本。

同时IP还与综合工具,架构空间探索工具及平台深度整合,确保需求多变,先进工艺,约束严格的挑战下SOC对IP的使用高效,稳定,安全,易用。 将这个事情交给EDA或像ARM这样的IP寡头做,这是相比SOC厂商自研和自选IP更加左移,更加高效的一种商业和技术场景。

IP开发和复用的另外一个考量因素是Fab。对于更先进的技术节点,如何给SOC提供高效的IP复用和开发机制,这是IP开发人员,SOC厂商和EDA合作伙伴之间的协作开发过程。它随着PDK的发展而发展,包括对RC提取,EM规则的更改,包括新的寄生/器件上限等,一直到工艺技术成熟为止。

Validation向左,Verification向右

来到了验证星球,随着上述IP解决方案的演化,IP复用,建模,VIP和生态发展以及软硬协同设计重新兴起,验证方法学也发生了很多相应的变化,传统verification是一个有限的逻辑问题,这是由仿真的机制决定的,靠有限空间的逻辑计算,理论上可以帮你找到你能想到的bug。但实际上芯片真实的工作场景要更chaos一些,保证质量不能只靠仿真,而且加上时间约束的话,这更加是一个不可能完成的任务。 这,就是验证3.0需要解决的问题。

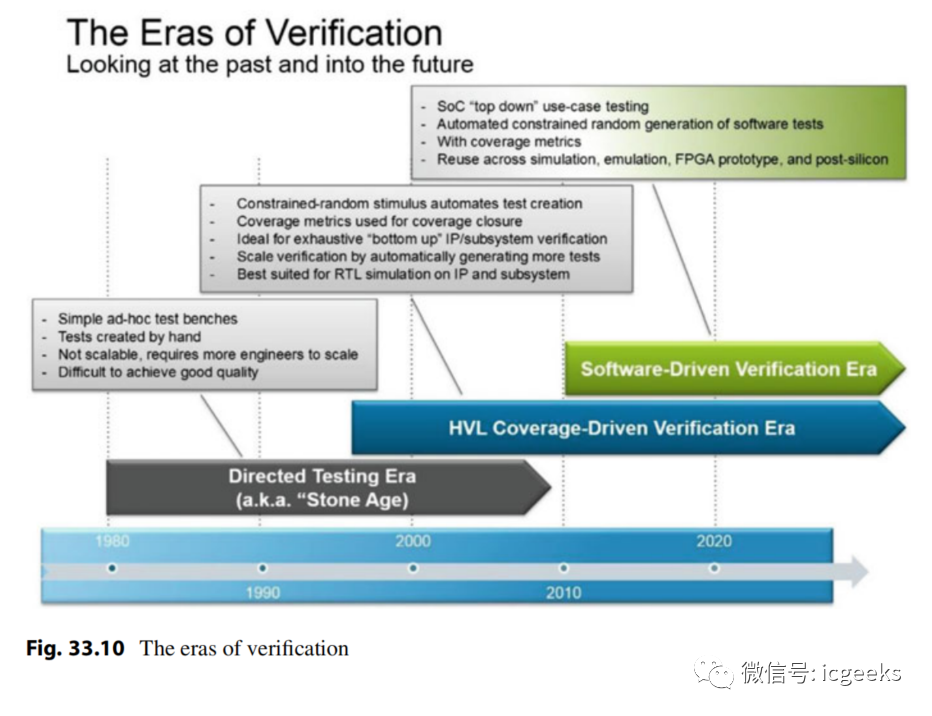

验证的早期 ,被称为石器时代 ,以直接的手工测试为主,这种方法扩展性极低,并且不能有效的保证质量。

在IP复用的年代 ,90年代后期,验证有了自己专属的语言和方法学,开启了SystemVerilog 和UVM的黄金时代。这个时代的两个重要武器是constrained-random stimulus automated test creation 以及coverage metrics driven coverage closure. 自动化和可扩展的程度大幅度提升,并使得VIP复用成为可能。但仍然是以bottom-up的验证策略为主。

在10年代 ,随着验证方法学进一步演化,top-down展现了完全不同的思路和格局,软件驱动的场景验证大放异彩。需要理解系统场景,用户场景,理解软件和硬件的协同。这是传统HVL方式无法企及的高度,随着simulation, emulation, FPGA原型验证,虚拟原型验证,validation的兴起,对自动化程度,工具使用,软件工程 还有设计方法都有很高的要求。

验证的目标也从传统的发现bug,找出所有的bug转移到保证芯片质量,进而在设计过程中内建质量 ,跨整个产品周期,在设计的每一步,最好是每一天,每个层级都能保证质量,向前迭代,一直往前走,避免返工。这样,走到最后,质量就是有保障的。

这两个目标是有本质区别的。 后者更加拟合我们现在所倡导的一种shift left的方法学。

具体体现在

-

将验证的工作跨整个产品周期,深度融合了持续验证的思想,包括系统级,架构级,pre-rtl,rtl, post-rtl,post-silicon,跨产品周期的软件验证,安全验证,这是时间维度的shift left, shift right

-

post-silicon validation向pre-silicon shift left,包括operational testing,user acceptance testing

-

传统verification的范围向系统级进一步扩展,跨越整个产品周期,而不仅仅是pre-silicon

-

TDD, 单元测试,可复用的IP/VIP平台,从传统的设计结束后验证才开始转向持续集成,将验证的工作融入设计交付的日常,各种不同的验证策略打散到工程全周期和设计深度两个维度。

-

从传统的在项目之初形成完备的验证计划,按计划执行到按sprint动态调整

(更多详细的解释和落地实践请关注本号内验证主题的相关文章)

进入物理实现的世界

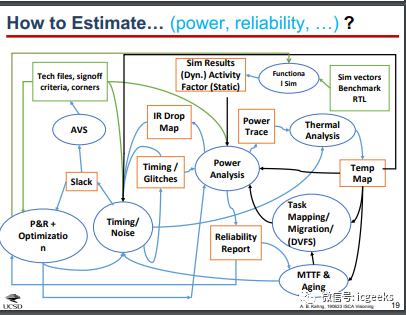

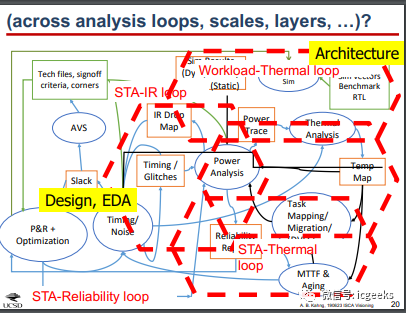

从这里我们开始进入物理世界的大门,它是连接逻辑世界和芯片制造的中段,中段的难点在于承上启下,需要帮助前端评估不同方案的PPAC,一起做upf, sdc co-design, pwr management, clk structure co-design,选择工艺,理解日趋复杂的工艺效应,制定实现策略和签核标准,理解IP,理解封装,选择合理的fp策略。从事物理实现的同学需要具备很多跨领域的knowhow,但更难的是, 物理世界的非常复杂的效应和指标无法独立考虑,是一连串chicken-egg的紧耦合 。

具体来说,譬如

-

PPAC的指标是跨越设计流程各个领域的,power delivery, timing signoff, cost,随着集成更加复杂,工艺尺寸降低,传统留margin的方式越来越不再适用,同时迭代一轮成本昂贵

-

综合及Place假定 zero skew vs. useful skew 优化依赖place结果

-

power产生IR drop进而影响timing/glitch/noise, 进而影响power

-

power产生热,热影响温度,温度影响DVFS偏差,进而影响power analysis

-

signoff标准制定依赖reliability,反之亦然

-

米勒效应导致timing window assumptions依赖crosstalk delay caculation, 反之亦然

-

chip signoff 定义 依赖library characterization,反之亦然

导致在一个长链条的设计流程中可预测性变差,无法预判最后的结果以及达到预期所花的成本,且迭代一轮时间更长,更加不利于方案探索阶段评估,从而导致设计更加不容易收敛,导致schedule不可控

之所以将上述影响之间的关系比喻为鸡和蛋,我是这样理解的,世界上本没有鸡也没有蛋,从一个恐龙蛋鸟蛋逐步演化到鸡这个物种,然后在有了鸡的那一刻便有了蛋,所有上述chicken-egg loop,不是因果关系,也没有先后关系,当有了这个状态的那一刻便有了所有的PPAC的结果,这会导致传统基于经验,基于推理,基于逻辑的设计方法不再有效,设计很难收敛,随着机器学习在EDA领域的应用日趋成熟,取而代之的是一种 渐进明细,迭代探索的方式,海量数据分析和大数据建模 (模型shift left + 一致性建模 + ML) ,而ML就是将状态逐步演化,提升可预测性设计,最终实现一个可以被signoff的状态,具体来说:

-

Physical Synthesis 从1.0到2.0,综合整合进RTL设计,后端模型整合进综合

-

自动fp,自动macro摆放,std摆放,通过ML及一致性建模预测对place, cts, route的影响

-

在fp阶段增加place功能

-

在place阶段引入DRC prediction model,clock tree analysis model

-

在global route阶段引入DRC prediction model

-

在CTS阶段增加skew prediction功能

-

将签核工具功耗分析的引擎集成进物理实现工具

-

将签核工具时序分析的引擎集成进物理实现工具

更进一步,还可以将物理设计的结果反标回架构探索阶段,方便前端设计更好的寻找PPAC友好的设计空间,将物理设计的结果反标回工艺开发阶段 ,也就是我们接下来要进入的DTCO 2.0

DTCO,打破死结

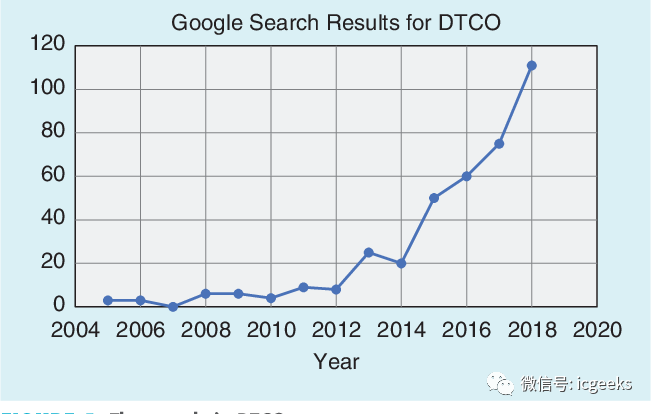

请大家继续跟随我的脚步进入工艺世界的大门,随着先进工艺节点持续演进,在10nm以下,设计和工艺的开发越来越紧密的交织在一起,传统按照先进行工艺开发,再移交给设计人员的方法已经不再适用,DTCO(design-tech-co-opt)的方法学在各个技术讨论中逐渐热起来。按照google搜索的热度,对于DTCO进行检索的论文数量自2012年后程指数暴涨,至今已上涨了10倍,其重要性略见一斑。

事实上,在过去的IDM时代,芯片厂商有自己的Fab,其工艺开发本来就是DTCO模式,但是在Fabless时代,特别是先进工艺制层上,DTCO面临不同的挑战和问题,演化出不同的需求和内涵。

具体来说,需要解决的一个本质问题就是,which device widths and model should fab offer to its customers for best power, performance, area scaling? 分析后端是很多鸡和蛋的loop,工艺对后端乃至整个设计有哪些重要的影响,却并没有在流片后将数据和影响反标回设计,也是其中最重要的一个鸡蛋哲学命题。

DTCO作为一种 反对传统流程无反馈,且极力缩短反馈链,以实现渐进明细的方法学 ,具体希望实现的目标如下:

Level 1: initially focused on design rule opt

Level 2: then captured standard cell logic layout

Level 3: now includes the entire physical design flow

Level 4:Bringing Design Technology and Architecture Closer Together

具体做法如下:

Level 1:TCAD建模与Litho仿真建立反馈闭环,形成spice model, design rule

Level 2: std cell的characterazation及PDK与综合/PR/RCX/STA/DRC/LVS的物理实现流程之间建立反馈闭环

Level 3: 将Level1与Level2之间建立反馈闭环

Level 4: 将流片后PPAC指标与架构设计之间建立反馈闭环

Level1&2是传统做法,Level3&4是现在备受关注的DTCO,反馈闭环建立的难度体现在 1. 流片成本 2. 物理实现的链条过长,研究主要围绕以下几个领域:

-

ML-powered, self-driving EDA tools and flows

-

ML-POWERED,SELF DRIVING EDA TOOLS AND FLOWS: restores access to hw imp; start with collaborative generation of data; unlocked by {design} +{tools} + {technology} = architects/designers + EDA researchers

-

Better oracles and constructive proofs of achievable PPAC (= DSE) at the absolute limits of a given technology and enablement

但通常DTCO只会在IP 级别发生,最常讲的是standard cell和technology的协同优化,单个产品像苹果华为的话,会有一些定制,其他的小公司,先进制程,即使是做一次轻微的工艺corner 偏斜定制,成本都不是小公司可以支持的,就有啥用啥了。

为了部落!EDA的力量与荣耀

好了,本次的芯际之旅到这里就要跟大家说再见了。

小E看着你们,满怀羡慕。市场的繁荣,先进的工具,丰富的架构,神奇的工艺,像是专门为你们准备的礼物,芯片设计的神奇被一层层打开,不同角色之间的壁垒被打破,你们只凭相同的目标,就能结交千万个值得干杯的ICer。

集成电路被设立为一级学科,EDA领域持续加大投入,更多年轻的朋友将会加入这个阵营,这,是最好的时代!

这是我们的世界!为了部落!为了IC的力量与荣耀!为了艾泽拉斯!

出征吧!

参考资料:

-

Handbook of Hardware/Software Codesign

-

A. B. Kahng DAC18

-

Machine Learning in VLSI Computer-Aided Design

-

https://semiengineering.com/merging-verification-with-validation/

-

https://semiengineering.com/verification-and-validation-brothers/

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2406期内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

模拟芯片|蓝牙 | 5G|GaN|台积电|英特尔|封装|晶圆

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 2 MediaTek天玑汽车平台推动汽车产业加速迈入AI时代,3nm旗舰座舱平台亮相

- 3 国内首颗,精准纠错!德明利TWSC2985系列:支持4K LDPC技术的存储芯片

- 4 OPPO 20周年,首次发布创新与知识产权白皮书