来源:本文转载自「

半导体百科

」

,谢谢。

<iframe allowfullscreen="" class="video_iframe rich_pages" data-cover="http%3A%2F%2Fmmbiz.qpic.cn%2Fmmbiz_jpg%2FcV40Me8cIZ1s3iacu77549noABH42QhIEibwOzMUnPO7PnhnqfaFrBrLXVhpkj3qTDEBKgmhOQ6JOTb1RQIzgsxQ%2F0%3Fwx_fmt%3Djpeg" data-mpvid="wxv_1599596505747800069" data-ratio="1.7777777777777777" data-src="https://mp.weixin.qq.com/mp/readtemplate?t=pages/video_player_tmpl&action=mpvideo&auto=0&vid=wxv_1599596505747800069" data-vidtype="2" data-w="1280" frameborder="0" scrolling="no">

</iframe>

由于新冠疫情的原因,2020年的第66届IEDM转为线上举办,但是这并没有影响IEDM对于半导体制造行业的重要性,今年的IEDM依然看点众多。2020 IEDM Press kit今天刚刚披露了会议的重点文章简介和会议环节,以下简单介绍一下本次会议中笔者认为较为有趣的几份技术更新。

40 kV Silicon Vacuum Transistor

文章编号5.2,“Demonstration of a ~40 kV Si Vacuum Transistor as a Practical High Frequency and Power Device,” W. Chernet al, MIT/ Harvard/ Massachusetts General Hospital。

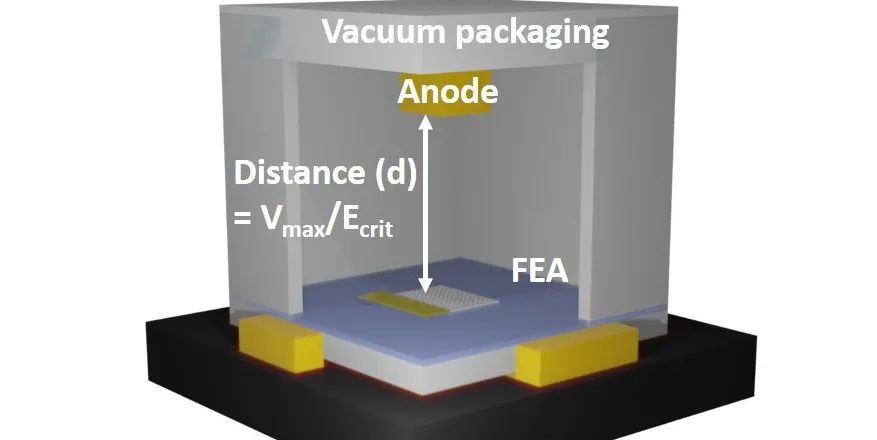

由MIT的团队带来的第一个工作在约40 kV的Si真空晶体管。这样的高电压电平通常采用SiC和GaN等宽带隙材料。该Si真空晶体管由门控场发射阵列(FEA,电子源),真空漂移区和金属阳极组成。电子通过隧道从门控场发射阵列发射到真空中并在阳极被收集。真空度决定了传输特性和高压隔离度。他们说,这些器件的高临界电场和无限制的载流子速度可以导致紧凑的高性能真空设备在所有指标上均能胜过固态器件,从而使其适用于一系列大功率和高频应用,也可以用作下一代X射线源。

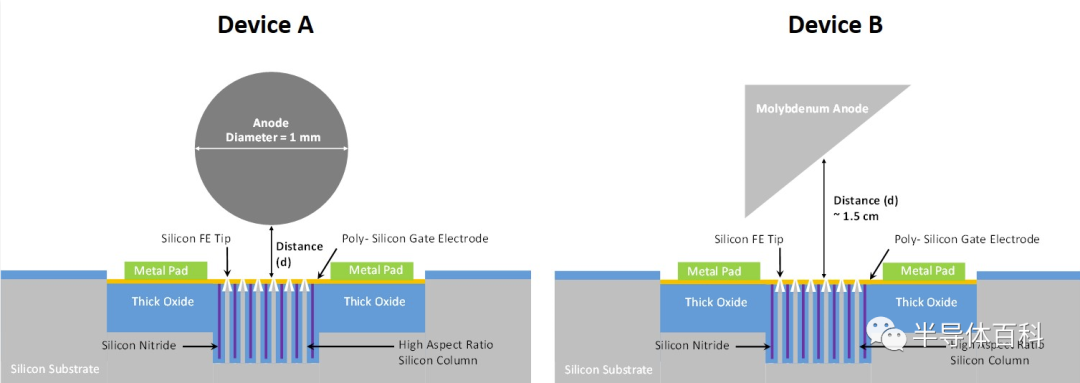

图1,不同真空器件测试设置的示意图。在这两种方法中,FEA电子源都位于真空中的金属阳极下方,从而形成了垂直器件。在器件A中,将直径为1mm的浮球阳极移动到距离FEA芯片一段距离d。在器件B中,固定的45度钼阳极距离FEA约为1.5厘米。

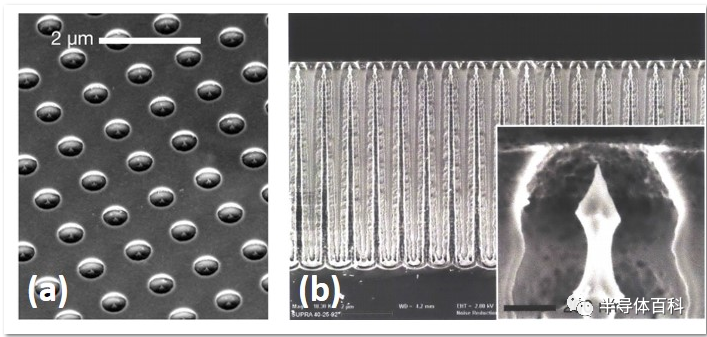

图2,(a)通过自对准制造工艺形成的〜200-300nm孔径的门控尖端阵列 (b)直径为200 nm的纳米线(约6-10μm高)。在该纳米线的顶部,存在一个尖锐的尖端,以集中周围多晶硅栅极的电场。

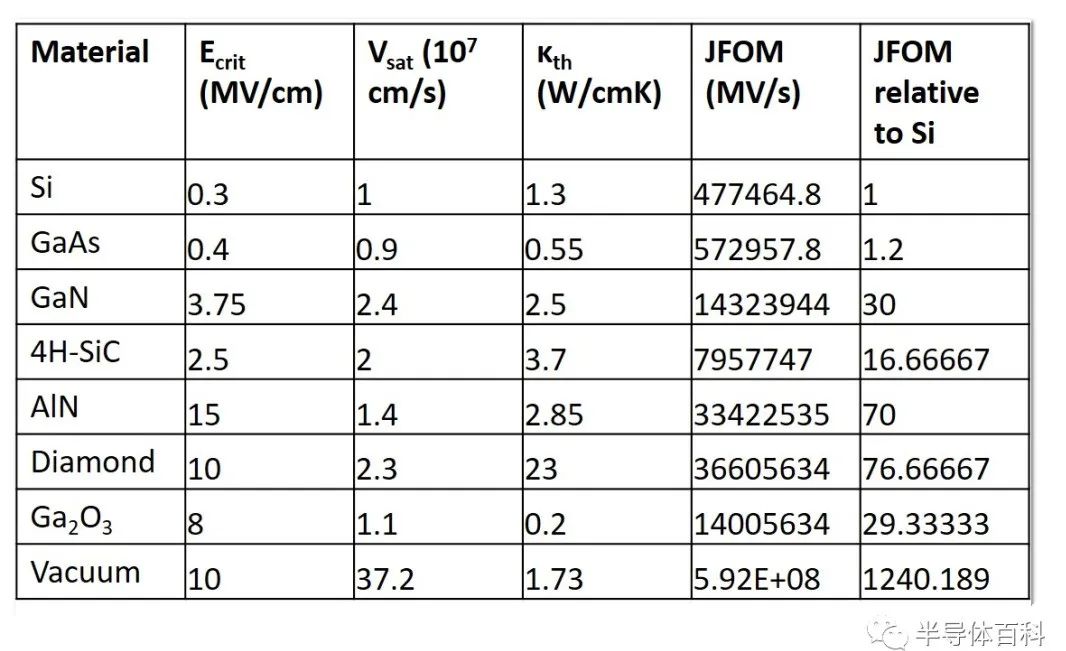

表1,表格比较了各种半导体材料的基本材料特性及其Johnson品质因数(JFOM,这是一种衡量半导体材料对高频功率晶体管应用的适用性的指标)。它表明,由于真空晶体管的高饱和速度和临界电场,其真空晶体管的JFOM远远超过了任何半导体。

Stacked NMOS-on-PMOS Nanoribbons

文章编号20.6,“3-D Self-Aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore’s Law Scaling,”C.-Y. Huang et al, Intel。

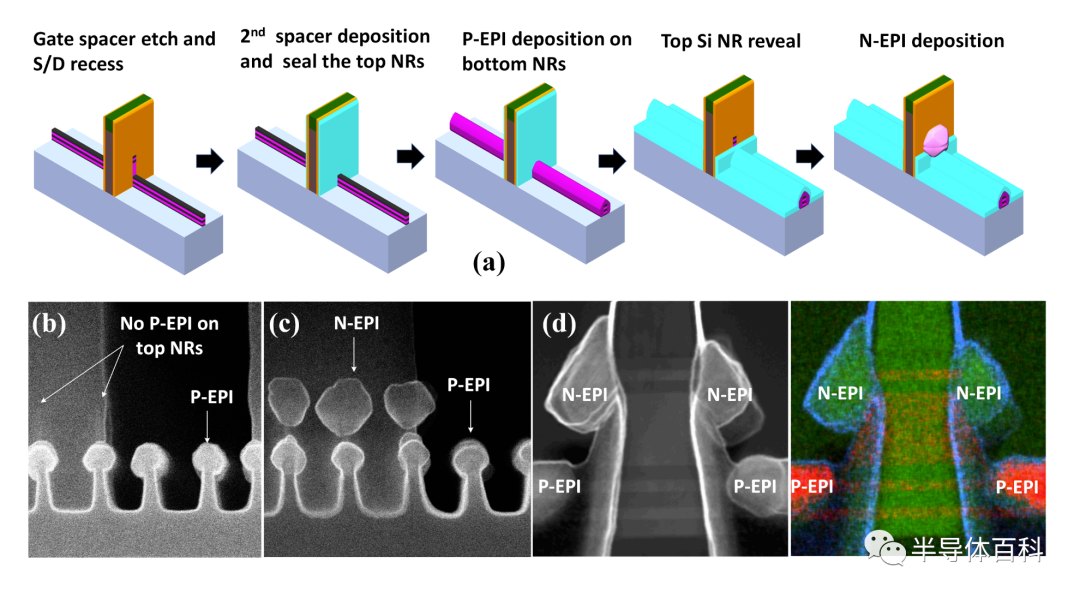

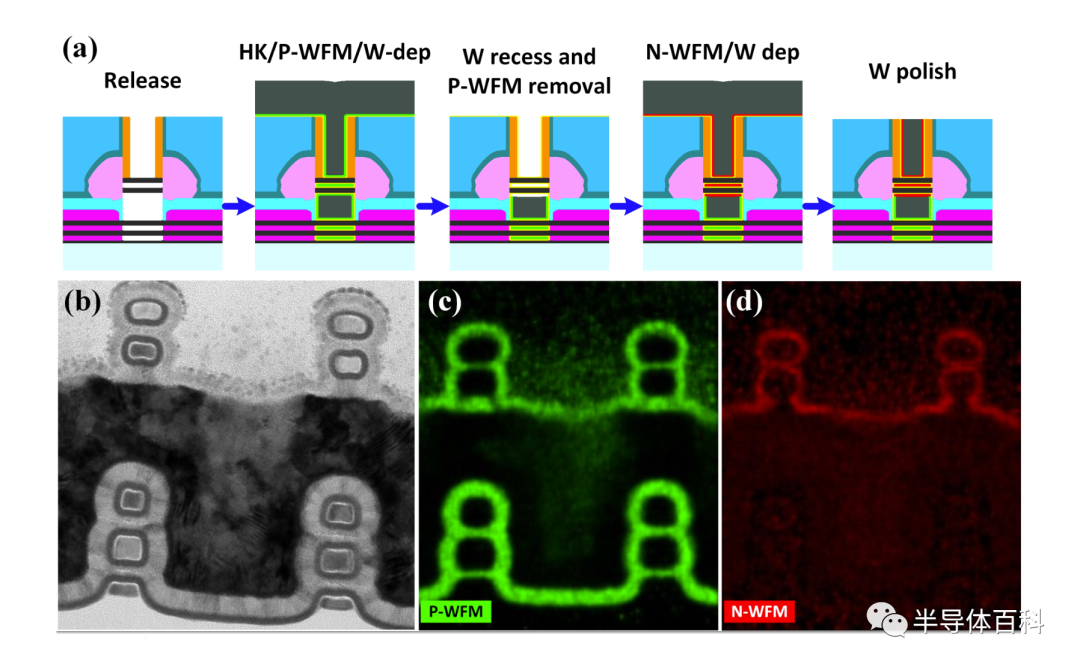

从平面MOSFET到FinFET,再到GAAFET,新颖的晶体管体系结构在推动摩尔定律预测的性能方面发挥了关键作用。英特尔研究人员认为这一发展的下一步:由多个自对准堆叠纳米片构建的NMOS-on-PMOS晶体管。该架构采用垂直堆叠的双源极/漏极外延工艺和双金属栅极制造工艺,能够构建不同导电类型的纳米片,以便可以对顶部和底部纳米带进行阈值电压调整。该方案获得了出色的电性(亚阈值摆幅<75 mV / dec)和DIBL(对于≥30nm的栅极,<30mV / V),并由于自对准堆叠而显着减小了单元尺寸。他们成功采用该架构制作了具有良好平衡电压传输特性的功能性CMOS反相器。

图2(a)GAA NMOS 堆叠在GAA PMOS上的3D示意图(b)该工艺流程(c)是具有40nm栅极长度的该CFET的TEM图像(d)3个Si纳米片的GAA PMOS 上堆叠2个Si纳米片的GAA NMOS的TEM图像。

图3(a)是垂直堆叠双S / D EPI工艺的工艺流程(b)在底部三个纳米片上选择性生长的P-EPI(c)在顶部两个纳米带上选择性生长的N-EPI(d)TEM和EDS图像显示在堆叠的纳米带晶体管上选择性生长的N-EPI和P-EPI。

图4(a)是垂直堆叠双金属栅极工艺的工艺流程;(b)TEM图像(c,d)N-WFM,P-WFM的EDS图像。

Large-Area Active-Matrix Microfluidics Platform

文章编号35.5

“Large-Area Manufacturable ActiveMatrix Digital Microfluidics

Platform for High-Throughput Biosample Handling,”H. Ma et al, Suzhou Institute/Acxell Tech/Hangzhou Linkzill Technology/Univ. Cambridge/ShanghaiJiao Tong Univ。

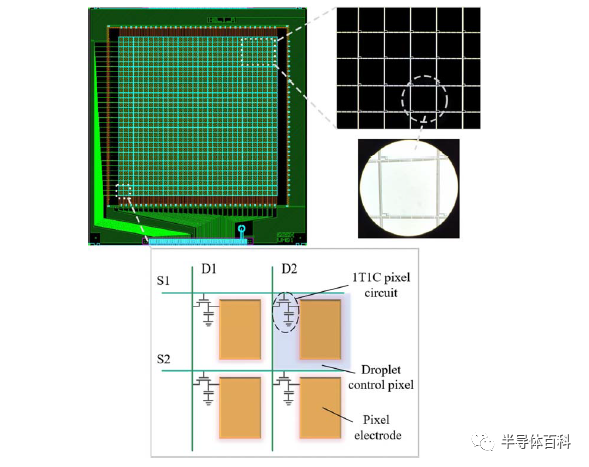

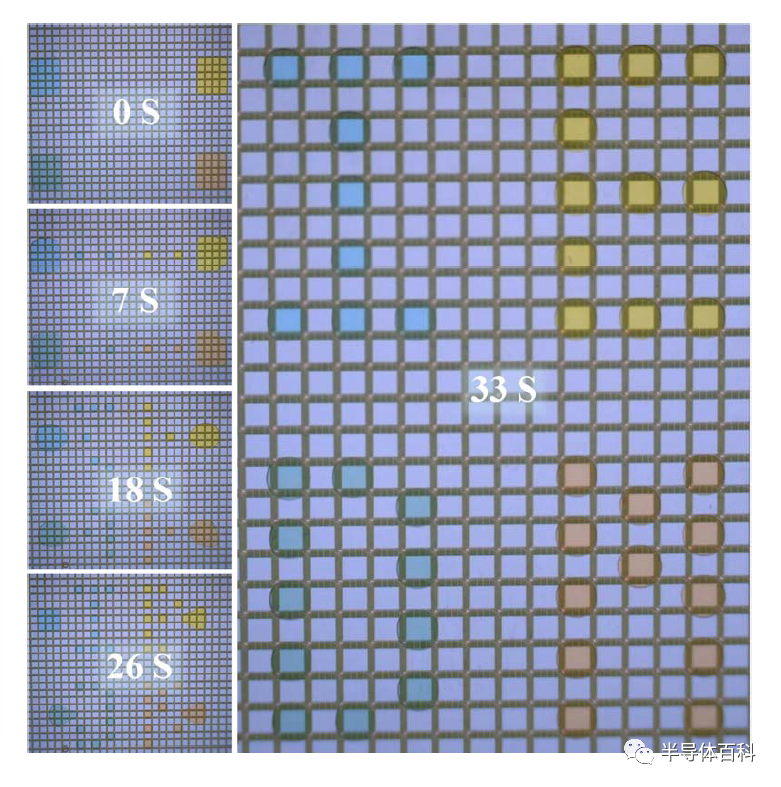

由中科院苏州医学工程技术研究所主导的基于电润湿(

Electrowetting)及多晶硅薄膜晶体管的

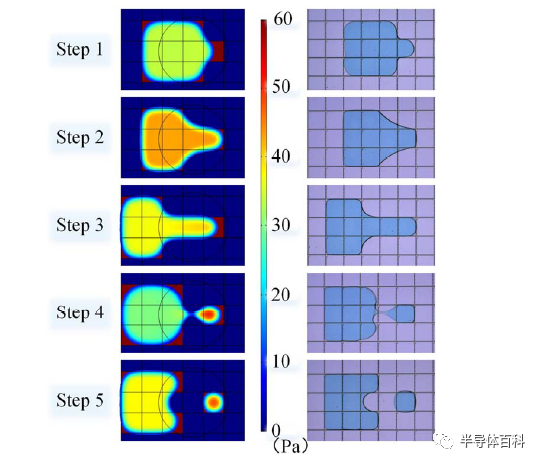

生物样品的可编程操作技术。电极阵列按顺序在特定位置施加电压信号,使得表面上的液滴跟随电场而移动,合并,混合和/或分离。该团队使用FPD有源矩阵技术制造了一个芯片,该芯片在10平方厘米的有源区域中包含一个32×32像素阵列(即电极阵列)。每个像素都可以单独或同时寻址,并实现了在单像素水平上约1%的体积变化系数的液滴操作。

图1,有源矩阵电介质上电润湿(AM-EWOD)器件的图像,版图和像素示意图。

图2,五步单滴生成方法,其中包含FEA模拟和真实设备图像。

图3,数字墨滴在AM-EWOD设备上形成“ IEDM”。 同时在芯片上实现并行墨滴生成和大规模墨滴处理。

当然作为半导体制造业最重要的会议,今年的IEDM上各家公司也都带来了他们对于逻辑微缩的新看法和技术,以下是重点环节预告,敬请期待。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2492期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

存储|晶圆|光刻

|FPGA|并购|Marvell|华为|功率半导体

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!