来源:内容来自半导体行业观察(ID:icbank)编译自

「IMEC」

,谢谢。

近年来,诸如二硫化钨(WS2)之类的2D材料在未来逻辑芯片的制造中可以发挥至关重要的作用。由于其卓越的性能,它们有望实现最终的栅极长度缩放,并因此可以扩展逻辑晶体管的缩放路线图。他们还可以通过启用紧凑的后端兼容晶体管,彻底改变我们对芯片架构的看法,从而模糊前端和后端之间的界限。

近年来,基于实验室的2D晶体管已经相当成熟,并且正在为其工业应用开发一条路线。同时,正在解决提高设备性能的剩余挑战。

在本文中,imec的项目总监Iuliana Radu解释了全球对这些材料的兴趣,尤其是它们对进一步扩展逻辑技术路线图的承诺。

2D材料是形成二维晶体的一类材料。在这种优雅的2D尺寸中,它们具有令人着迷的电,热,化学和光学特性。这些材料中最著名的是石墨烯,一种六角形的蜂窝状碳原子片。石墨烯具有出色的机械强度,高的热电传导性和奇特的光学性能。

但是,二维材料的探索已经远远超出了石墨烯。化学式为MX

2

的一类过渡金属二卤化物具有多用途的性质,可与石墨烯互补。

与石墨烯不同,二硫化钨(WS

2

),二硫化钼(MoS

2

)和其他一些具有广泛的带隙,使其成为天然半导体。根据其化学组成和结构配置,原子上薄的2D材料也可以归类为金属或绝缘材料。由于其卓越的性能,二维材料的机会已经出现在多个应用领域,包括(生物)传感,能量存储,光伏,光电和晶体管缩放。

在芯片制造中,诸如WS

2

和MoS

2

之类的2D半导体已成为替代晶体管导电通道中“Si”的候选材料,他们拥有巨大的优势?与Si相比,基于2D的场效应晶体管(2D-FET)有望更不受短沟道效应的影响-短沟道效应已成为进一步扩大Si晶体管尺寸的主要障碍。

确实,随着基于Si的晶体管沟道越来越小,即使栅极上没有电压,电流也开始在其上泄漏。随着每一代技术的发展,这种效应被称为短沟道效应,情况也变得越来越糟,危害了进一步的栅极长度定标。当今的主流晶体管技术FinFET在某种程度上抵消了这种影响。在这种晶体管架构中,鳍状沟道区可以做得更薄,并且栅极在不止一侧上包围沟道。这使得栅极电压更容易控制基于Si的沟道内载流子的流动。即将到来的向纳米片晶体管的过渡-栅极现在四面八方围绕着通道-进一步建立在这个想法的基础上,提供了更好的静电控制。但是,当缩放到3nm以上时,问题再次出现。这就是高机动性WS

2

和MoS

2

可以支持的地方。它们可以被构造成几个甚至单个原子层,从而提供了提供非常薄的沟道区域的可能性。这极大地限制了电流流动的路径,从而在关闭设备时使电荷载流子更难泄漏。因此,它们有望实现最终的栅极长度缩放(10nm以下),而无需担心短沟道效应。

为了支持这些承诺,我们在imec的团队最近进行了一项设计技术协同优化(DTCO)研究。我们展示了2D-FET如何以堆叠的纳米片晶体管体系结构为最可能的插入点来进一步扩展逻辑器件技术的扩展路线图。

2D材料可用于构建紧凑的back-end-of-line switches

2D半导体的应用可能会超出高性能晶体管的范围。另一个潜在的应用领域包括性能和面积限制较小的低功率电路。例如片上电源管理系统,信号缓冲器和存储器选择器。最重要的是,通过启用小型后端兼容开关,可以使用2D材料彻底改变芯片的后端(BEOL)。

芯片制造大致可分为两部分:

在其中构建晶体管的前端(FEOL),以及通过多层互连连接晶体管以形成功能电路并传输功率的BEOL。随着传统晶体管的缩放变得越来越具有挑战性,科学家一直在寻找在BEOL中添加晶体管和小型电路的方法,从而在FEOL中节省了一些面积。但是,这样做只能使用可以在相对较低的温度下集成的材料,以免损坏设备及其下方的互连。使用2D半导体应该可以做到这一点。使用基于2D的晶体管而不是其他一些“ BEOL”候选材料的另一个优点是具有建立n型和p型器件的潜在能力,这是CMOS逻辑的必要条件。

基于实验室实现的超大规模2D晶体管表现出出色的性能

但是,我们是否可以通过实验来构建这些超大规模2D-FET,并且它们是否能够履行其在性能方面的承诺?近年来,科学家探索了各种MX

2

材料。最初,基于MoS

2

的设备被证明是最成熟的,实验报告的最高迁移率值接近理论值200cm

2

/Vs。最近,基于WS

2

的FET也可能显示出竞争性结果。从理论上讲,它们具有更高的性能潜力。在改善接触电阻和增强器件性能方面取得了进展。

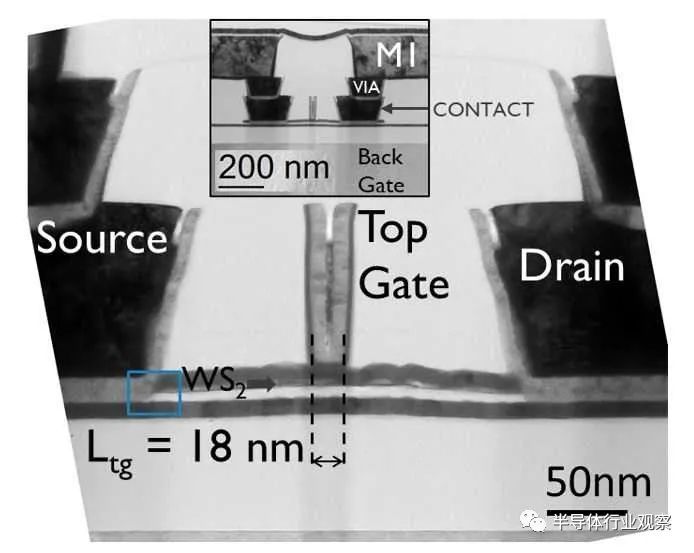

例如,在imec,我们的团队可以演示功能齐全的2D-FET,其沟道厚度仅为1-2个单层,长度为30nm。我们还显示了通过使用双门控设备结构改善的静电控制。传统的FET顶部只有一个栅极,而双栅极晶体管同时具有顶部和底部栅极,当连接时,可以改善对沟道的静电控制。

如果我们能够大量生产2D-FET,那么它们就能在逻辑技术路线图中找到它们的位置。这将是采用工业技术的关键。这意味着我们需要能够将这些设备带出实验室,并使用行业标准的生产工具将它们集成在300mm晶圆上。

Imec为在300mm集成流程中采用这些2D材料奠定了基础。此流程用于研究各种处理条件的影响并努力提高性能。例如,可以使用金属有机化学气相沉积(MOCVD)演示2D材料在300mm晶圆上的高质量生长,该过程是通过化学反应在表面沉积晶体的过程。使用该工具,可以在整个300mm晶圆上以单层精度控制厚度。实验表明,较高的沉积温度(即950°C)对镀层的结晶度和缺陷率有有益的影响。

图:使用300mm工艺制造的2D器件的TEM图像。

但是,更复杂的晶体管体系结构(例如堆叠的纳米片,或者更深层的路线是互补FET(CFET))可能需要替代性的沉积技术。对于处理热预算有限的后端电路也是如此。因此,Imec研究了其他沉积技术,并探讨了使用转移工艺的可行性–允许将2D通道移动到已经部分制造的300mm Si衬底上。

目前,单个设备的性能要比报告的实验室设备低一个数量级,而300mm的集成流程则用于了解工艺影响并确定集成障碍。沟道材料的质量和缺陷率的控制仍然是提高器件性能的最大挑战。第二个障碍是源极/漏极触点的接触电阻,需要降低到可接受的水平。第三,需要开发综合模型以实现上述设备架构设计,并具有内置的实际流程假设。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2626内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备|模拟芯片

|射频|传感器|美国|光刻

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!