来源:内容由半导体行业观察(ID:icbank)编译自「

anandtech」,谢谢。

从2019年开始,晶圆厂就开始有限度地将极紫外(EUV)光刻技术用于芯片的大批量制造(HVM)。在当时,ASML的Twinscan NXE系列光刻机能够满足客户的基本生产需求,然而整个EUV生态系统却还没做好所有的准备,其中影响EUV的因素之一就是缺少用于光掩模的防护膜(protective pellicles for photomasks),这限制了EUV工具的使用并影响了产量。

幸运的是,由于最近推出了可用于生产的EUV防护膜,因此防护膜的状况终于得到了改善,而且情况有望在未来几年得到改善。

近年来,凭借其Twinscan NXE EUV光刻工具取得了长足进步,ASML改善了EUV光刻机的光源性能,可用性时间和生产率。其业界同行也做了很多工作,以使使用EUV设备的大批量制造(HVM)成为可能。尽管如此,EUV生态系统仍需要进一步发展。半导体供应链面临EUV的最臭名昭著的挑战之一就是防护膜(pellicles )的开发,在两年前,这种防护木(pellicles )还没有面世,这也就是为什么TSMC和Samsung Foundry必须发明如何使用没有保护膜的EUV扫描仪的方法。

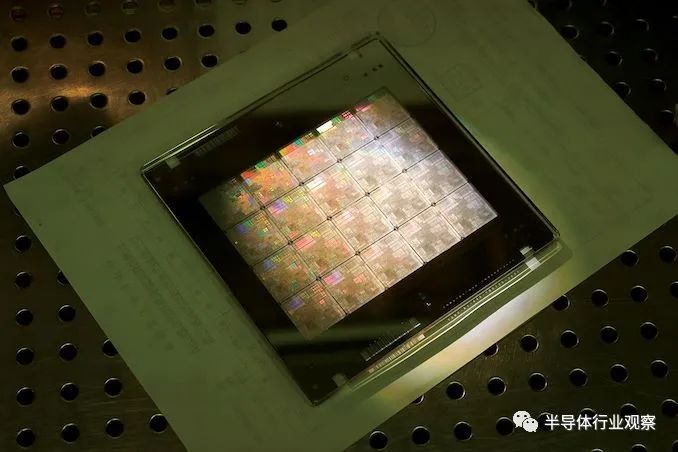

A 16nm TSMC Pellicle With Reticle

薄膜(Pellicle)通过将其与可能落在其表面上的颗粒隔离开,从而在芯片生产流程中保护6×6英寸光掩模(掩模版),否则在这个过程中可能会损坏它们或在生产中给晶圆造成缺陷。每个EUV工具的reticle要花费30万美元,因此芯片制造商迫切希望能找到新的方法保护它们的晶圆免受微粒甚至EUV辐射本身的损害,因为这样可以降低成本。同时,降低与收益率相关的风险也许更为重要。

与此同时,对薄膜(pellicles)的需求则根据制造商和所用光掩模的类型而有所不同。英特尔以其大的CPU裸片而闻名,它倾向于使用单裸片,这意味着粒子引入的仅一个掩模缺陷会自动杀死整个裸片。同时,如果使用25个die的光掩模,粒子加法器将“仅”导致产率降低4%(一个死die),这就是为什么对于较小的芯片和多die的光掩模,无需使用防护膜(pellicles)即可摆脱困境的原因。

在得知没有人能够保证超复杂的EUV扫描仪100%不含有害颗粒后,该行业开始为EUV工具开发保护膜,这是相对较晚的时间,这就是为什么它们在2019年尚未准备就绪的原因。

与深紫外线(DUV)光刻设备一起使用的光掩模膜盒是常见且便宜的。相比之下,由于EUV的光掩模与DUV的光掩模不同(EUV掩模本质上是250到350 nm厚的堆叠,在基板上具有40到50个交替的硅和钼交替层),因此这种标线的防护膜也大不相同。特别是,极紫外光的波长非常短,这意味着其防护膜有许多要求,使其不易生产且价格昂贵。EUV防护膜必须非常薄,不应影响掩模版的反射特性,应具有较高的透射率(透射率越高,扫描仪的生产率越高),应维持较高的EUV功率水平并承受极端温度(从600ºC至1,000ºC的未来)。

IMEC的Emily Gallagher说:“大多数材料在13.5nm EUV波长上都具有非常强的吸收能力,即使选择了大多数EUV透明材料,其膜也必须非常薄才能达到90%的透射率。”“这种薄膜通常不能保持足够的强度,无法在所需的尺寸下独立放置。此外,EUV扫描仪的环境与许多材料不兼容,会使防护膜经受抽气-排气循环的作用。”

根据SemiEngineering的说法,迄今为止,已经出现了许多EUV防护膜选项包括:

-

ASML于2019年推出了首款EUV防护薄膜,并将该技术授权给三井化学,该公司计划在2021年第二季度开始批量销售。此后,ASML改进了防护薄膜;

-

Imec已公开了其基于碳纳米管的防护膜的测试结果;

-

Graphene Square, Freudenberg Sealing Technologies (FST)和一些大学正在开发自己的防护膜;

到目前为止,只有ASML设法为实际可用的EUV工具创建了商业上可行的防护膜。ASML的防护膜基于厚度为50 nm的多晶硅。早在2016年,他们就展示了在模拟175W光源上的78%的传输率。目前,ASML可以出售透射率达88%的防护膜。不久之后,三井将开始大量供应此类防护膜。

ASML推出的,由金属硅化物制成的最新原型展示了90.6%的透射率,0.2%的不均匀性以及在400W光源下反射率小于0.005%的情况。

ASML防护薄膜产品经理Raymond Maas在接受Bits&Chips.nl采访时说:“此次升级支持我们的路线图,最终将使电源功率高达400瓦。” “在该功率水平下,薄膜被加热到600ºC,而多晶硅则无法承受。”

相比之下,Imec的原型防护膜的透射率为97.7%。实际上,从长远来看,当可以使用更高级的光源时,将需要更复杂的防护膜,这就是Imec基于碳纳米管的防护膜将发挥作用的地方。

“很少有材料具有超过90%的高EUV透射率的潜力,甚至更少的材料可以同时兼容超过600W的EUV功率。此外,防护膜必须坚固,才能悬挂在大面积的光罩上(〜 110mm x 140mm),”来自Imec的研究人员Joost Bekaert说。

不幸的是,目前尚不清楚Imec的基于碳纳米管的防护膜何时准备就绪。

现在,台积电(TSMC)和三星(Samsung Foundry)发明了使用EUV光刻工具生产较小芯片的多die掩模,而不需要防护膜的方法,但是这种方法存在风险,因为任何颗粒添加剂都可能成为导致产量下降的缺陷。此外,这样的方法对于较大的芯片和单die光掩模来说是有风险的,因此,防护膜对于使用EUV工具制造大型die至关重要。也就是说,无论光掩模的尺寸大小如何,都需要使用防护膜来提高EUV产量并降低整个领域的风险。

总体而言,EUV防护膜的使用和改进将是一个循序渐进的过程。由ASML开发和制造的初始防护膜,不久将由三井制造,足以满足当今的某些需求,但其透射水平仍有改进的空间,这由ASML和Imec的下一代原型证明。由于这些机器将拥有更强大的光源,因此也需要更好的防护膜来应对未来的扫描仪。但是,由于这样的防护膜具有许多无可争议的优点,它们将被芯片制造商使用,因为即使以一些生产率为代价,它们也可以帮助提高产量。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2632内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备|模拟芯片

|射频|传感器|美国|光刻

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!