三星8nm工艺经过验证背后,对摩尔定律没信心的表现

2017-10-19

19:04:28

来源: 半导体行业观察

点击

10月18日消息三星半导体宣布已经于近日完成了8nm LPP制程工艺的验证工作,比预计计划提前三个小时,三星表示不久之后便可以开始量产8nm制程的芯片产品。相比目前的10nm制程工艺,8nm工艺可以让芯片的功耗降低10%,而芯片面积却可以降低10%。

8nm是7nm的过渡?

8nm LPP工艺的全称是8nm Low Power Plus,是基于目前的10nm工艺改进而来的,号称可以提供更好的性能表现以及更高逻辑门密度。相较10 纳米制程技术,新推出的8 纳米LPP 制程技术可使芯片能效提升10%,芯片面积降低10%。

三星表示,即将量产的8nm LPP工艺制程将会是7nm投产之前最先进的工艺制程,该工艺基于已经有实际生产经验的10nm芯片的工艺技术,可以提供比当前10nm产品更好的性能和可扩展性。有分析师表示三星的8nm LPP制程工艺不仅将用于三星以及高通的ARM处理器制造,更是为7nm制程作铺垫。

虽然三星目前已经具备了8nm LPP制程工艺的批量生产能力,但短期内产量可能并不能满足高通的需求,外媒普遍认为骁龙845仍将采用三星的10nm工艺制造,骁龙855才会使用8nm LPP工艺。

高通高级副总裁RK Chunduru也此进行祝贺,他表示“8nm LPP工艺来得很快,比起现有10nm工艺提供更好的性能以及更小核心面积”。

一些糊弄人的数字游戏?

三星在技术研发上面的影响力是毋庸置疑的,但是从这个8nm节点的描述上看来,似乎这是一个基于10nm技术的修改版,这与过去对于节点命名的方式有点不相符。联想到早前Intel在其举办的制程大会上的发言,我们很倾向于相信三星的这个做法是一个“数字游戏”?

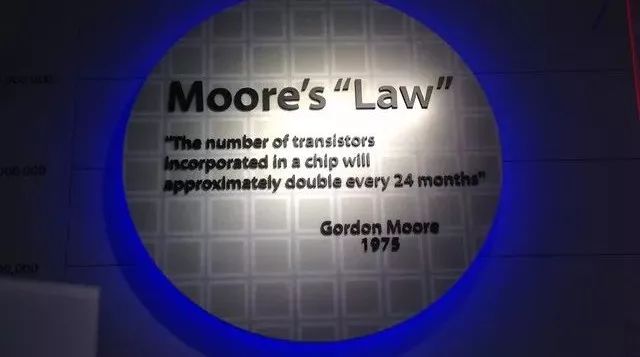

在日前的大会上,英特尔制程专家Mark Bohr强调,观芯片创新历史,业界这么多年来一直遵循摩尔定律,并按前一代制程的0.7倍对新制程节点命名,这种线性升级正好带来晶体管集成密度翻番。因此,出现了90纳米、65纳米、45纳米、32纳米——每一代制程节点都能在给定面积上,容纳比前一代多一倍的晶体管。

但是最近,也许是因为进一步的制程升级越来越难,一些公司背离了摩尔定律的法则。即使晶体管密度增加很少,或者根本没有增加,但他们仍继续推进采用新一代制程节点命名。结果导致制程节点名称根本无法正确体现这个制程位于摩尔定律曲线的哪个位置。

行业亟需一种标准化的晶体管密度指标,以便各个厂商公平竞争。客户应能够随时比较芯片制造商不同制程的产品,以及不同芯片制造商的同代产品。挑战在于,半导体制程以及各种设计日益复杂。

英特尔方面的看法是启用曾经流行但一度“失宠”的一个指标:它基于标准逻辑单元的晶体管密度,并包含决定典型设计的权重因素。尽管任何设计库中都有各种标准单元,但是我们可以拿出一个普及的、非常简单的单元——2输入 NAND单元(4个晶体管),以及一个更为复杂、但也非常常见的单元:扫描触发器(SFF)。这能够推导出之前接受的晶体管密度测量公式。

通过采用这个计算公式,行业可以厘清制程节点命名的混乱状况,从而专心致志推动摩尔定律向前发展。

当然,我们也并不是无条件信任Intel的这套算法。但考虑到Intel作为制程工艺的先锋,其创始人更是摩尔定律的提出者,他们的看法有一定的参考意思。

业界需要从架构探讨出路

三星的这个命名的“无奈”,从侧面反映了摩尔定律放缓,业界在新材料发展乏力,制程微缩受限的现状下,更需要从架构上寻找新的出路。

在昨日于香港举办的高通4G/5G峰会上,高通QCT总裁Cristiano Amon也表示,现在制程微缩的步伐正在减缓,过去通过工艺升级带来产品性能提升的周期越来越大,他们在未来会更注重于架构,注重在DSP/CPU/GPU的协同研发,提升产品性能。英特尔之前也表示,他们的做法是在同一个工艺节点内做细微升级,逐步改进工艺带来性能提升。例如在10nm的时候他们会推进10nm+和10nm++。

因此回到三星这个新工艺,他们在性能上的提升,是毫无疑义的,但对于命名的方式,半导体行业观察认为需要给出更多的技术细节自证,或者遵循Intel的命名方式,整个行业统一规范,免去客户甚至普通消费者的困惑。

责任编辑:星野

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 2 破除AI落地难题!英特尔全新软硬件平台,助力企业AI创新

- 3 晶圆厂中的“超纯水”,你真的了解吗?

- 4 三方联合,上海国际汽车电子与半导体应用展览会将于明年4月在上海举办