来源:内容由半导体行业观察(ID:icbank)

编

译自semiwiki,谢谢。

在最近于旧金山举行的国际电子器件会议 (IEDM) 上,台积电进行了富有洞察力的演讲,分享了他们对封装路线图目标和挑战的愿景,以满足对更高芯片集成度、更高性能和更高互连带宽不断增长的需求。本文总结了演讲的重点。

2.5D 封装使多个die能够横向靠近放置,在die和封装基板之间存在的硅中介层上制造的die之间具有信号重分布互连层 (RDL)。硅通孔 (TSV) 提供与基板的连接。

该技术的 TSMC 实施被表示为衬底上硅片 (Chip-on-Wafer-on-Substrate:CoWoS),正如十年前引入的那样,使用封装中的多个 FPGA die来扩展有效门数。

高带宽内存 (high bandwidth memory:HBM) 堆叠芯片作为 2.5D 集成的一个组成部分的出现为系统架构师提供了内存层次结构和处理器到内存带宽的新替代方案。

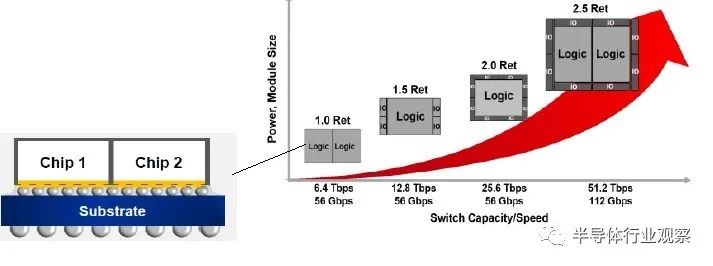

2.5D 技术的开发投资增加,现在使硅中介层面积大大超过“1X 最大”掩模版尺寸,以适应更多(和更多样)处理、内存和 I/O 芯片组件(又名“小芯片”) 。

额外的封装制造步骤将本地“沟槽电容器”整合到中介层中。氧化物-多聚-氧化物-多聚材料层填充沟槽,多晶硅连接到 RDL 电源金属。由此产生的去耦电容大大降低了电源电压降。

台积电还开发了替代技术,用嵌入有机中介层的相邻芯片之间的局部“硅桥”(CoWoS-L) 代替全面积硅中介层,从而降低成本(尽管 RDL 互连尺寸放宽)。

同时,对于非常低成本的应用,对比传统晶圆级芯片级封装 (WLCSP) 所能支持的更高 I/O 数量的裸片的需求导致了一种新技术的发展,该技术通过“重构晶圆”,在其上可以制造重新分布到大量 I/O 凸块。

这种集成扇出 (InFO) 技术最初是为单芯片开发的(作为类似 WLCSP 的产品)。然而,在重构步骤之前,该技术的应用很容易扩展到支持相邻放置的多个异构芯片的 2.5D 集成。(稍后将讨论 InFO_oS 技术。)

3D 芯片堆叠技术也发展迅速。如上所述,在 DRAM 存储器芯片层之间制造 TSV,在 TSV 的另一端连接“微凸块”,实现了令人印象深刻的垂直堆叠水平——例如,在 HBM2e 配置中,8 个存储器芯片加上一个基本逻辑控制器芯片。

类似地,InFO 通孔(位于重构晶圆材料中的基础裸片外部)使额外的微凸点裸片能够垂直堆叠在基础 InFO 裸片上方——例如,逻辑裸片顶部的存储器裸片。

3D 堆叠技术的最新进展是在两个芯片表面之间采用无凸点的“直接键合”。应用独特的热+压缩工艺,两个模具表面连接在一起。不同管芯上的金属焊盘区域扩展以形成电连接,而两个die上的邻接电介质表面被接合。支持面对面 (F2F) 和面对面 (F2B) 芯片方向。表面的平整度和均匀性(翘曲)要求苛刻;存在于表面上的颗粒尤其成问题。台积电将他们的 3D 封装技术称为系统集成芯片,或“SoIC”。

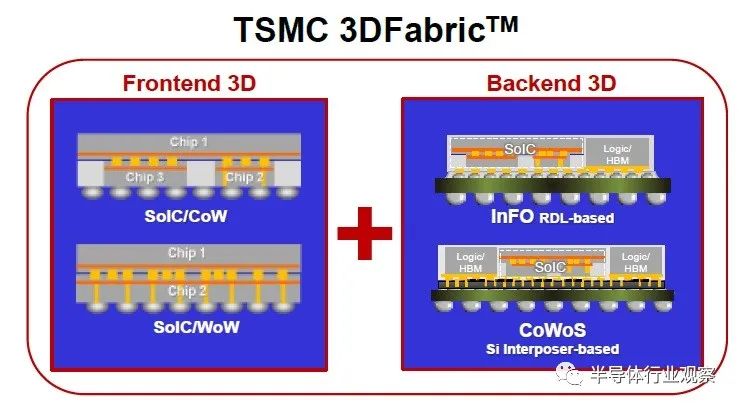

随着产品架构师正在探索这些封装技术的可用机会,人们越来越有兴趣将“前端”3D 堆叠 SoIC 配置与 2.5D“后端”(InFO 或 CoWoS)RDL 图案化和组装相结合。台积电为其整套先进封装产品赋予的集体品牌是“3D Fabric”,如下图所示。

在 IEDM 上,台积电分享了他们为这些技术提高性能、功率效率、信号带宽和散热的策略。(主要关注点是 SoIC 的键合技术。)

-

将 Si 中介层的封装尺寸增加到 3 倍的最大光罩尺寸

-

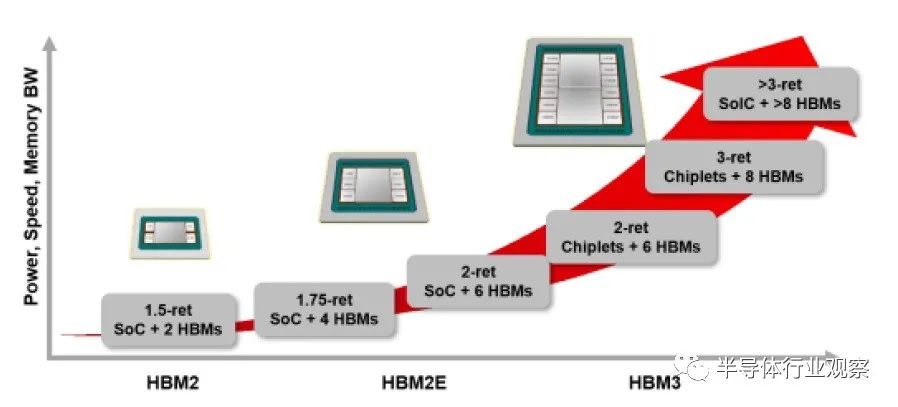

期望堆叠的 SoIC 芯片将与多个 HBM 堆叠集成

最初的 InFO 产品是作为 WLCSP 的演变,首先作为单个die,然后作为基础芯片,在顶部添加另一个连接到 InFO 通孔的芯片。台积电还在扩展 InFO 产品,以支持嵌入在重组晶圆中的多个相邻芯片;然后制造 RDL 层并添加微凸块以连接到基板(InFO-on-Substrate,InFO_oS)。要支持的 InFO_oS 配置的投影如下图所示。

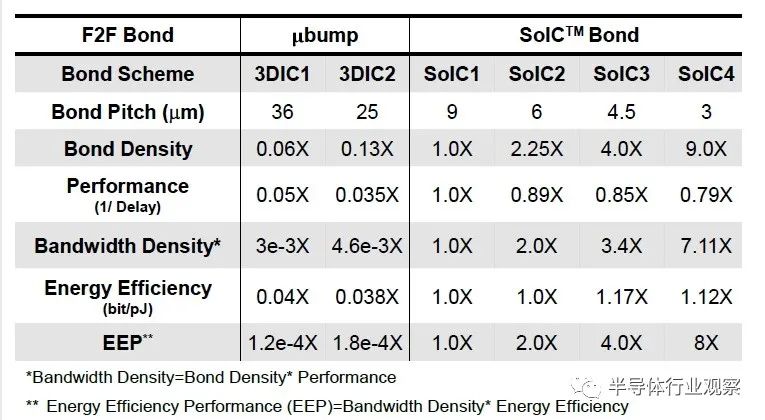

下面显示了 3D 封装开发的路线图,然后是一张说明关键技术重点的表格,即缩放(F2F 或 F2B)堆叠连接的键距。

用于微凸块技术演变的键距(和其他指标)包含在上表中的 SoIC 直接键合测量中以进行比较。

如上表所示,台积电定义了一个新的(相对比较)指标来表示 3D 堆栈键合技术的路线图——“能效性能”(EEP)计算。请注意,EEP 中的目标增益是由键距缩放的激进目标驱动的。

EEP = (bond_密度) * (性能) * (能效)

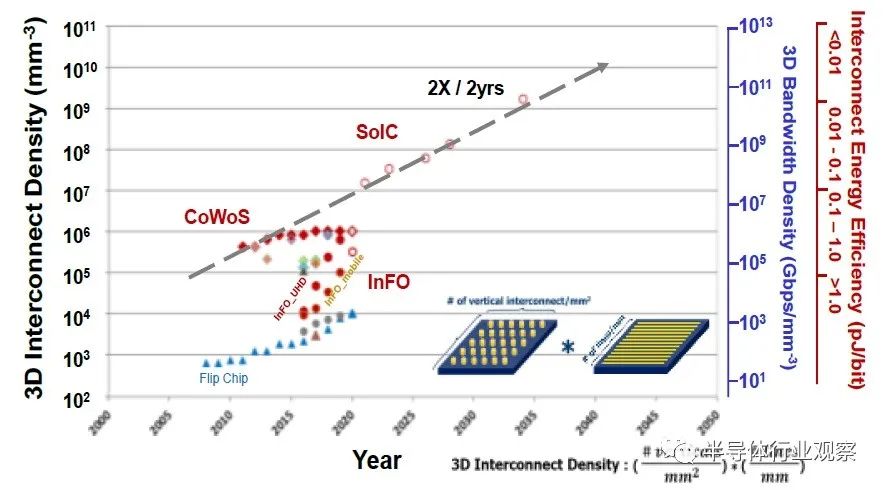

与摩尔定律相关的 IC 缩放非常相似,3D 键合缩放在性能与互连密度之间存在权衡。而且,就像摩尔定律一样,台积电路线图的目标是争取每一代 EEP 提高 2 倍。

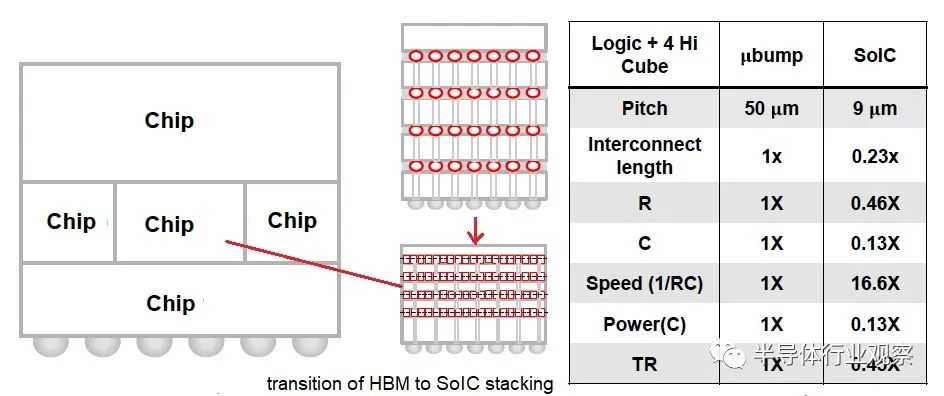

为了说明未来 3D 堆叠的潜力,台积电提供了一个三高堆叠结构的示例,如下所示。

请注意,假设未来的 HBM 堆栈将从堆栈内的微凸点连接技术迁移到键合连接——图中还显示了这种转变在性能、功率和热阻 (TR) 方面的优势。

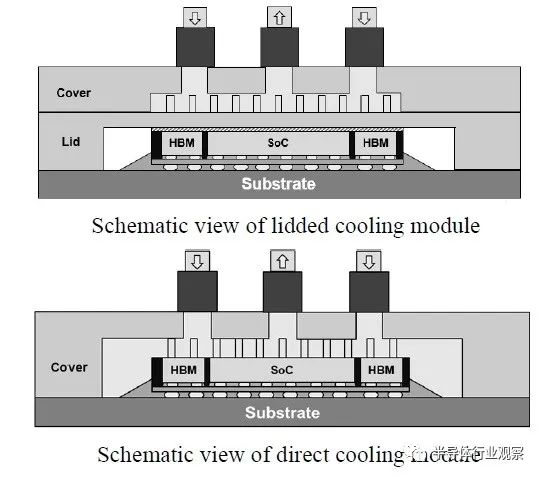

说到热阻,台积电强调了低热阻的键合工艺和建议的 3D 堆叠配置的设计分析的重要性,以确保所有芯片的结温 (Tj) 保持在限制范围内。

IEDM 演讲提到了台积电正在进行的额外研究,以评估液体冷却技术选项。如下图所示,“微柱”可以蚀刻到与组件结合的硅盖中,甚至可以直接蚀刻到芯片中,以进行水冷。

先进的 2.5D 和 3D 封装技术将为系统设计人员提供独特的机会来优化性能、功率、外形(面积和体积)、散热和成本。台积电分享了他们 2.5D 和 3D 配置的开发路线图。

2.5D 的重点将继续支持更大的基板尺寸,以实现更多(异构)芯片集成;对于专注于成本与性能的市场,不同的中介层/桥 (CoWoS) 和重组晶圆(InFO 技术选项可用。

3D 堆叠技术将获得最大的发展重点,重点是缩放界面键距。每一代 SoIC 所产生的“EEP 提高 2 倍”是新的“超越摩尔”半导体路线图的目标。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2909内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!