FinFET的潜在继任者,揭秘VTFET晶体管

来源:内容由半导体行业观察(ID:icbank) 编译自allaboutcircuits ,谢谢。

去年 12 月,IBM 和三星宣布了一种新的晶体管架构,据说可以挑战传统的 FinFET。我们就该项目与 IBM 的两位主要研究人员进行了交谈以了解详细信息。

传统的硅场效应晶体管 (FET) 在性能、速度和功率效率方面正逐渐接近其极限。2021 年底,IBM Research 和三星电子之间的合作产生了一种新型晶体管,可以帮助规避与现有互补金属氧化物半导体 (CMOS) 相关的一些与缩放相关的限制。

据 IBM 称,这些被称为垂直传输纳米片场效应晶体管 (VTFET:vertical-transport nanosheetfield-effect transistors ) 的新型晶体管可以显着改善性能和面积缩放,与缩放的 FinFET 架构相比,可能会减少多达 85% 的设备能耗.

我们采访了 IBM 的 Brent Anderson 和 Hemanth Jagannathan,他们是创造 VTFET 的两位研究人员,以了解有关新晶体管及其制造工艺的更多信息。

半导体研究高级技术人员 Brent Anderson(左)和首席研究人员 Hemath Jagannathan(右)。

问:在我们开始讨论你最近的工作之前,你能告诉我们一些关于你在 IBM 的角色吗?

Brent Anderson: 我于 91 年加入 IBM,此后从事多项技术工作,并在十多个技术节点担任过领导职务。我与这里的 VTFET研究团队合作了五年多,在此之前,我推动了其他逻辑节点的技术设计点和目标。

大约十年前,我开始了VTFET 的工作,然后将其带入了我们的硬件开发周期。因此,当谈到 VTFET 时,我是大局观的一站式商店,而 Hemanth 是工艺流程和硬件结果方面的专家。

IBM 研究人员在轨道上携带掩模版,将 NXE3400 EUV 工具送入轨道后面。

Hemanth Jagannathan: 我 15 年前加入 IBM,从事平面和 FinFET 技术的高 K 金属栅极技术的早期材料研究。我管理的制程技术小组负责为IBM 研究院的各种逻辑技术引入新材料。

从硬件研究的早期开始,我就一直担任 VTFET 项目的硬件技术专家和开发经理。在我的角色中,我与 IBM 和三星的同事携手合作。我已经推动 VTFET 团队通过功能性硅硬件演示将这个项目中的新颖想法从纸上带入实践。

问:最近,您参与了一个导致第一个垂直传输纳米片场效应晶体管 (VTFET) 的项目。是什么激发了您的团队创造这些设备?

安德森: 十年前,我们已经知道我们将面临横向 FET 的扩展挑战,当我们试图从一个节点缩小到另一个节点时,我们可以看到障碍。在横向FET 中,您有一个栅极和隔离物(spacers),以及触点。缩放它们时存在物理限制,这实际上限制了 40nm 以下的缩放。

VTFET 的动机是找到一种解决方案,使摩尔定律在这个 40nm 接触栅极间距 (CGP:contacted gate pitch ) 之外继续缩放,这是从一个晶体管的栅极到另一个晶体管的栅极的最小距离。当我们移动到垂直方向时,我们可以使栅极更长,源漏和间隔物更厚,从而降低电阻和电容。因此,我们不仅变得更小,而且还能够获得更高的性能。

问:新半导体架构的主要优势是什么?它的特点是什么?

Anderson: FinFET 取代了平面,因为它们具有更好的栅极控制,并且 CGP 可以从大约 90nm 缩小到48nm。然而,随着我们继续扩展 CGP,我们遇到了许多问题,尤其是在门控方面。这就是纳米片的用武之地——50nm 到 40nm CGP。

使用纳米片,我们摆脱了量化,实现了对 Fin 厚度的更严格控制,并移动到围绕通道的栅极,这意味着我们可以进一步缩小 CGP。然而,在大约 40nm 的栅极间距处,我们的空间不足。例如,栅极长度变得难以控制。

使用 VTFET,栅极完全包裹在鳍片上,现在鳍片(片材)是垂直的,我们现在可以制作任意长的栅极。将栅极与源极和漏极隔离的垫片更厚,源漏也更厚,从而降低了电阻。

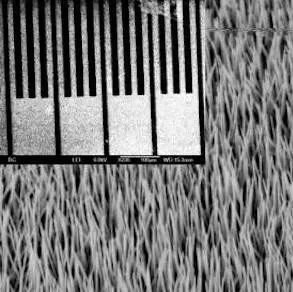

VTFET 晶圆。

VTFET 的其他独特特性是与底部源漏、顶部源漏和栅极的接触。因为有更多的空间,我们可以使触点更大,降低电阻值并将它们移动得更远,从而获得更低的电容和非常好的良率。而且,由于现在的功能是垂直的,现在有更多的空间分隔功能,使我们能够扩展技术向前发展。

为了隔离横向 FET 中的电路,我们需要插入一个虚拟隔离门(dummy isolation gate),这是一种特殊的门,可以将一个电路与下一个电路电隔离并浪费大量空间。使用VTFET,我们改为引入隔离相邻电路的小氧化物沟槽。这意味着更多的扩展可能性,因为我们不需要额外的虚拟门来隔离各个电路。

总结 IBM 多年来引入的关键技术的时间表。

Jagannathan:

CGP 是我们用来比较不同架构的指标。我们展示了用于 VTFET 的 CGP,它比目前生产的产品更具侵略性,这对于第一篇硬件研究论文来说是非常不寻常的。翻转电流方向(相对于衬底)为触点和定义栅极长度的自由度创造了更多空间。它还优化了器件电容,并允许在没有虚拟栅极的情况下对相邻晶体管进行独特的隔离。我们将这种独特的隔离技术称为零扩散中断 (ZDB:zero-diffusion break )。

问:这种架构与传统的FinFET 技术相比如何?

Jagannathan: 在开发新的晶体管架构时,您需要更高的密度,这样您就可以在给定的区域内集成更多的晶体管,并获得更高的性能和能源效率。当横向 FET 架构(例如 FinFET)被迫安装在 40nm CGP 内时,器件的特性将明显下降。您将被迫使用薄垫片、非常短的栅极长度和有限的触点空间。所有这些挑战都将对性能和功率产生直接影响。

使用 VTFET,由于零扩散中断 (ZDB),我们能够获得更高的密度。我们可以将电路拉得更近,去除伪(dummy)栅极,并减小栅极间距。由于触点现在很大,我们可以独立调整触点的大小,并将顶部和底部触点的电阻降低近一半。

电流流过的 VTFET(左)与横向 FET(右)晶体管的比较。

该结构本身具有独立的旋钮来调节各种参数,因此我们也能够实现电容减少 50%。这本身就是巨大的,因为与同一规格下的 FinFET 器件相比,它的性能提高了两倍。在您希望在性能与能源之间进行权衡的情况下,您可以获得同等性能,但功耗降低 85%。所以这是非此即彼的,但如果产品需要,您可以介于两者之间。

此外,通过垂直翻转栅极和沟道,我们还能够优化间隔尺寸,以便您可以拥有更大的间隔,这意味着您可以承受更高的电压,从而拓宽器件的工作范围。

问:您在开发晶体管时遇到了哪些主要挑战?你是如何克服它们的?

Anderson: 转向垂直方向会极大地改变开发过程。例如,垂直垫片(spacers)的定义与横向垫片的定义非常不同。顶部的源漏加垫片也非常新颖和不同。

我们选择早期解决的基本特征之一是自对齐。对于零扩散中断,我们使用新的自对准技术而不是图案化引入了非常窄的沟槽。这需要不同的集成要求,即使必要的工具实际上与我们今天使用的类似。

VTFET 晶圆特写。

问:我们什么时候会看到新的晶体管上市?

Anderson: FinFET 是当今市场上最先进的技术。Nanosheet预计将在短短几年内问世,并持续几个节点。VTFET 的时机是在纳米片之后,要经过很多年才能进入市场。我们提交了这份文件,为行业做好准备,因此当它推出时,基础设施将可用,这将是一项成功的技术。

手机是最有可能推出此类产品的最大市场之一。

问:这些晶体管是 IBM 和三星合作的成果。两家公司在资源和专业知识方面为该项目做出了什么贡献?

Jagannathan: 我们与三星等合作伙伴以及我们的供应商有着非常紧密的生态系统。对于这个项目,IBM 和三星工程师在纽约奥尔巴尼共同办公,每天并肩工作。三星是半导体技术的大批量制造商,虽然 IBM 目前不再生产自己的芯片,但我们在研究和创新方面拥有深厚的专业知识。

纽约奥尔巴尼 NanoFab South 热压粘合 (TCB) 工具的研究员。

问:您认为 VTFET 是扩展摩尔定律的关键吗?

Jagannathan: 我们展示的 VTFET 技术显示了更高性能、更低能耗和更高密度的潜力。我们相信 VTFET 是一种强有力的候选后纳米片,并为未来几年摩尔定律缩放提供了光明的未来——以及最近在单片 3D 和芯片堆叠技术方面的创新。

问:实际实施这些晶体管的下一步是什么?

安德森: 第一步是与行业分享,以获得反馈和接受。我们现在需要继续开发这项技术,使其更加成熟。除了逻辑晶体管之外,我们还分享了其他特性的早期结果,其中进一步优化很重要。

未来,我们还计划发表涵盖SRAM、逻辑电路等的设计论文。在我们准备好投入生产之前还有很多步骤,随着我们继续推动技术向前发展,这将在接下来的几年里填满。当我们在 IEEE 国际电子器件会议(IEDM)上展示它时,反馈非常好。

Jagannathan: IBM 内部和外部的工作对于VTFET 的实际采用和实施至关重要。随着我们开始更多地了解 VTFET,我们渴望看到业界以及设计界、供应商和设备界的反应。所有这些都有望开启一次良好的对话,以进一步成熟我们的观点。

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2974内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 ISEDA 2024,东方晶源带您探索EDA前沿技术!

- 2 智能边缘时代,英特尔大有可为

- 3 两巨头垄断的芯片市场,跑出了一家中国企业

- 4 品英Pickering发布新款40/42-788系列微波多路复用器模块 提供最多通道数的微波多路复用开关