半导体制造大PK 工艺or大佬 谁定输赢?

当今的半导体行业竞争激烈,而晶圆制造作为关键的环节,厂商之间的竞争也是空前激烈,特别是英特尔(Intel)、台积电(TSMC)、三星(Samsung)和格罗方德(GlobalFoundries)这几个行业大佬,在争取大客户方面更是用尽浑身解数,明争暗斗得不可开交。总的来说,眼下的半导体制造之争,主要表现在两方面:一是工艺技术,即FinFET和SOI;二是工艺节点,即16/14nm、10nm和7nm。

工艺技术之争

1. FinFET为主流

目前,FinFET(Fin Field-Effect Transistor,鳍式场效应晶体管)是所有大型晶圆制造厂商采用的主流先进工艺。在传统晶体管结构中,控制电流通过闸门,只能在闸门的一侧控制电路的接通与断开,属于平面架构。在FinFET架构中,闸门成类似鱼鳍的叉状3D结构,可于电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流,也可以大幅缩短晶体管的闸长。

2. SOI崛起

上世纪80年代,业界就有人提出了SOI(Silicon-On-Insulator,绝缘体上硅)工艺设想,当时,伯克利的胡正明教授也指出,当摩尔定律走到极限的时候,能够推动半导体产业继续向前发展的技术会有两种,一是FinFET,另外一个就是SOI。

SOI是CMOS工艺的特殊版本,二者最大的不同在于衬底,CMOS的衬底是导电的,而SOI采用绝缘体硅工艺,其衬底是不导电的,而导热性又比较好,因此,可以利用这一特性,通过特殊方法,弥补其在击穿电压特性上的不足,从而实现高功率电路。

特殊结构使SOI电路具有较高的跨导、低寄生电容、减弱的短沟效应和较为陡直的亚阈斜率。SOI技术的另一特性是耐高温,在高温环境下,SOI器件性能明显优于体硅器件,这是因为高温下与体硅器件相比,SOI器件的源和漏结面积小,可使漏电流降低很多。FD-SOI(全耗尽绝缘硅)工艺在射频(RF)和物联网芯片方面的优势明显。

虽然SOI工艺成功之路历经坎坷,但目前已经渗透入主流市场。苹果的iPhone 6s就采用了SOI工艺射频芯片,此外,Intel和IBM也正使用SOI工艺来推动硅光子技术的发展。

相比FinFET工艺,FD-SOI晶体可节省20%的管芯成本和50%的氧化埋层成本

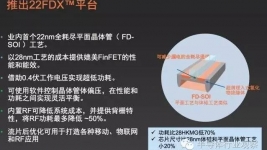

目前,格罗方德是SOI工艺的主要推进者,该公司声称,其FD-SOI(全耗尽绝缘硅)在未来4年内的销售量将超过FinFET。为此,格罗方德推出了22nm的“22FDX”SOI平台,并表示这项工艺在能实现更低功耗的同时,还具有与28nm工艺相似的成本优势,并且性能可与FinFET技术相媲美。

格罗方德的22nm FD-SOI项目于2016年下半年在德国德累斯顿工厂投产,为此已投资2.5亿美元。ARM、Imagination、意法半导体、飞思卡尔、VeriSilicon、IBS、Semeria、Soitec等都表达了支持,宣布将会采纳该工艺。

以前按照摩尔定律,大家总认为芯片成本会不断降低,但是在28nm以后,如果采用FinFET工艺,单个晶体管的成本不降反升,所以,是成本让摩尔定律出现了危机!而这正是“22FDX”SOI平台要解决的问题,该技术最有价值的一点就是它提供的性能和功耗堪比FinFET,但成本却与28nm相当。

FinFET可以做到10nm和7nm级别,FD-SOI也具有相同的能力,并且成本更低。格罗方德认为,22FDX正好处于14LPP/LPE和10LLD之间,该公司的下一个目标是实现与10nm FinFET相对应的性能,但是可以降低20%~30%的芯片成本。

工艺节点之争

在智能手机处理器芯片方面,不管是高通、联发科,还是代工企业台积电和三星,均在力推10nm和7nm工艺,尤其是10nm,台积电已经明确表示将会在年底生产10nm芯片,而联发科(Helio X30)和华为海思(麒麟970)也表示会在年底采用台积电10nm FinFET技术代工。不过从10nm FinFET代工技术来看,台积电和三星暂时还难定输赢,台积电夺下了苹果的订单,三星拿下了高通的订单,两家力均势敌,因此,双方将在7nm一决高低。

从台积电和三星公布的7nm代工服务时间表来看,台积电将会在明年第一季度开始设计定案,并在2018年初量产;而三星也称将在2019年第四季度量产。此外,从设备方面来看,台积电和三星均采用了ASML的EUV光刻机,台积电将于2017年第一季度采用ASML的光刻机,部分用于7nm芯片制造,部分用于2020年以后的5nm芯片制造;三星则计划在2017年第二季度采用ASML的EUV光刻机,而EUV光刻机有助于提升7nm、甚至5nm芯片的良率。据统计,目前英特尔有5台EUV光刻机,带4台订单;台积电也有5台,带2台订单;三星有3台,带3台订单;格罗方德有1台,带1台订单。

虚实相间的工艺节点

实际上,不管是台积电还是三星,他们的芯片制造工艺线宽都没有达到实际的14nm/16nm,台积电客户透露,台积电目前量产的16nm苹果A10处理器,其实与英特尔的22nm制程差不多,高通也认可这一观点。

台积电目前的16nm工艺,原本计划和英特尔一样叫做20nm工艺,因为该制造工艺的最小线宽和量产的前一代20nm工艺差不多,只不过采用了FinFET技术,不过,对于同样的制造工艺,三星却称其为14nm,其实并非严格意义上的14nm,只是性能上等效14nm,因此,台积电也跟随三星虚称为16nm。

据了解,除了台积电、三星、格罗方德以外,目前制造工艺技术最先进的英特尔也存在虚报现象。台积电的16nm制程实际最小线宽是33nm,16nm FinFET Plus线宽则为30nm,而三星第一代14nm的最小线宽是30nm,14nm FinFET则是20nm,英特尔14nm制程经过测量后发现,分别是20nm和24nm。

对于究竟是几个纳米线宽,目前没有行业标准,太多产品没法定义。英特尔每年在研发上花100亿美元,而台积电才20亿美元,可以看出英特尔在技术上仍然领先,但领先的幅度已慢慢缩小。而对客户而言,看的不仅仅是技术领先与否,包含良率、耗电量等因素都在考量范围之内,而非只有制程一项因素而已。如果光从数字就可评断,那先前苹果A9芯片门事件也不会闹得沸沸扬扬了,毕竟三星的整体数字是优于台积电的。

很多半导体人认为,摩尔定律终究会终结,只是早晚的问题。我甚至怀疑,芯片真的会做到5nm吗?做到现在这个程度已经很厉害了,做到5nm设备成本太高。所谓摩尔定律终结在5nm时期,就是终结在成本上,其在技术层面实现是可以的,但真的实现的话,投片的成本太高,而性能的提升有限,所以意义不大。

国际电机电子工程协会(IEEE)指出,微处理器中的晶体管体积,将在2021年停止缩小。从时间方面来看,2021年,正好是台积电、三星等芯片代工厂5nm芯片开始量产的时候,如果IEEE预估准确的话,那就意味着摩尔定律终结在5nm工艺。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“ 半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

点击阅读原文,查看更多半导体高薪职位

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 当我拿出 4 卡 GPU 测试 Ansys 流体仿真,阁下该如何应对?

- 2 英飞凌2024汽车创新峰会:揭秘全球汽车芯片No.1供应商的创新与布局

- 3 收购GaN Systems后,英飞凌氮化镓迎来新突破

- 4 ADI携4大产品线亮相上海慕展,引领智能边缘行业新升级

- 5 迈来芯亮相上海慕展,解析技术创新布局与中国本土化战略