Chiplet面对的头号挑战

2021-05-08

14:00:18

来源: 半导体行业观察

来源:内容来自「

CTIMES

」,谢谢。

当延续摩尔定律的开发重点,也就是单一芯片晶体管数量的世代更迭仍因技术受阻而放缓,未来芯片市场逐渐开始拥抱小芯片的设计思维,透过广纳目前供应链成熟且灵活的先进制程技术,刺激多方厂商展开更多合作,进一步加速从设计、制造、测试到上市的流程,让更多高效节能的芯片与物联网成真。

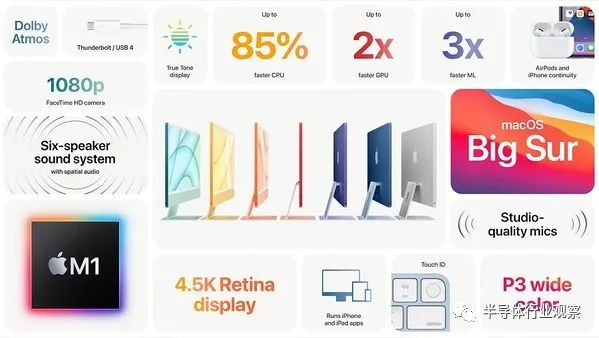

要说目前市场上最主流的芯片设计,必非「系统单芯片(SoC)」莫属。就这点,近年最广为热论的焦点就锁定苹果2020年推出基于Arm架构的自制芯片M1,而日前盛大举行的苹果2021年首场全球新品发布会中,最新一代iMac更揭晓为继MacBook之后采用M1的第二波产品之一,SoC更被点名,它就是iMac超轻薄吸睛外型的设计关键。

苹果M1把CPU、GPU、记忆体、I/O等元件全部整合在同个芯片上,目标是针对芯片性能、功耗和尺寸(PPA)全面进一步提升,结果确实也达到了整体系统效能优化的突破性成果。iMac除了尺寸更轻薄,在效能方面,CPU最高增加了85%,GPU最多提升至两倍,就连备受瞩目的AI机器学习,甚至能升级至三倍。

采用SoC设计的优势就是这么诱人,可以一次满足常被谈到的芯片性能三大指标,在在彰显其在芯片设计坐稳主流地位的关键。

但问题是,半导体发展至今,不仅负责不同功能的各类元件种类更多,包含如5G等无线通讯、AI加速,以及智能应用所需的语音、影像、温度感测等功能,这些在以往并非设计所需。

这些元件带给先进制程的生产挑战也更为严峻。晶体管是更小了,但整体系统却因需要整合更多元件而变得更大,良率会因此下降—想像一下,越大的靶,中枪阵亡的机率更高;开发成本也正变得越来越昂贵,不论是时间或资金,都导致意欲跟进新兴市场的IC业者难以跨越这道竞争门槛。

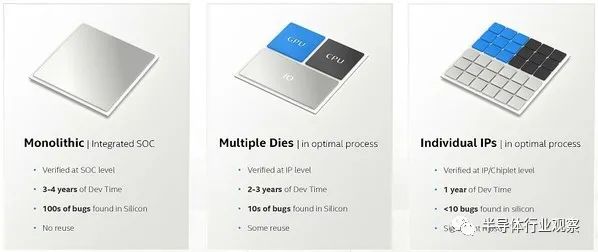

因此,考量未来产品应用的需求转变,以及目前制程技术的显见瓶颈,摩尔定律关注的晶体管密度与闸极微缩,很可能不再是未来芯片开发的首要重点,更有可能的是,芯片设计的灵活性、整合性和即时性将成为一股新风潮,从SoC这种单片(monolithic)的设计思维,趋动迈向模组化(modular)与异质性(heterogenous)的方向发展,这不仅能最大程度活化现有的供应链资源,更重要的是,可以更顺利地因应物联网对芯片的爆炸性需求。

小芯片趋势的进展速度非常惊人。市调机构Omdia就相当看好小芯片市场,2020年时他们预估,小芯片在半导体制造领域将在未来四年以九倍的速度成长,2024年产值达到58亿。未来,半导体产业也能借此回复到芯片每两年推新进展的经济循环。

小芯片架构的应用范围极广,包含MPU、GPU、PLD以及SoC都能导入这项新的设计思维。目前全球有越来越多半导体厂商与国家级研究单位开始采取这条另辟蹊径的芯片开发策略,甚至包含曾经对多芯片模组(multi-chip module;MCM)十分不以为然的Intel,它现在可是摇身变成小芯片市场的主要开发者之一,而且持续积极号召产业伙伴投入开发更多基于小芯片的产品。

Intel曾经坦言,早在开发双核处理器Pentium D和四核处理器Core 2时,他们就采取了将两颗小芯片放在同一芯片上的做法,前者用的是Pentium 4,后者是Core 2 Duo 。因为M2M架构可以减少设计复杂度、相关问题以及把问题复杂化的情况,而这些却是用单片核心(monolithic core)设计必须面对的固有问题。

小芯片架构把目前的主流设计思维分区解构,问题因此由繁化简,不过若想达到系统效能、成本与尺寸的极致优化,却也不是把大芯片切割再拼贴就能满足,小芯片的未来发展,主要就看半导体厂商的封装技术与介面连接技术。

Omdia分析师Tom Hackenberg就指出,小芯片采取的策略是用更多芯片来增加晶体管数量,刚好避开了摩尔定律在单一芯片上放更多晶体管的发展途径,利用封装,就能把多个小芯片整合起来。

显见封装技术无疑是开发小芯片时首先浮现的先决考量。在这个领域,Intel与台积电是长久以来的两大名将,双方对市场与专业技术常有所见略同的洞察,因此解决方案也不可免地互别苗头。在2.5D封装,分别提出了利用桥接互连的EMIB以及导入中介层的CoWoS技术,在3D封装则有Foveros和InFO技术。

有了这些先进封装技术,小芯片的应用要拓展与创新增添了许多可能,同时,现阶段产业也在努力达成小芯片开发的另一个目标,就是晶粒之间(D2D)的介面连接技术,目标是增加小芯片之间的传输频宽,同时确保这些偕同运作的功耗更省电,也就是精进小芯片设计的效能与功耗表现。

市场上现有的几个D2D介面解决方案都聚焦在实体层(PHY)。Intel就与美国国防部DARPA紧密合作,发展开源的AIB(Advanced Interface Bus)Pipeline架构,近期也公开了AIB 2.0的初步规格,不仅要增加每通道的IO数量,微凸块(microbump)的尺寸也要更小,其矩阵面积可以比上一代标准还小一半,整体频宽密度就能提升六倍。

AIBPipeline架构的开源性质也显示了硬体界的新气象,AIB 2.0的规格就是由Google号召成立的CHIPS联盟(CHIPS Alliance)宣布推出,成员还包括三星、阿里巴巴、威腾(Western Digital) 、明导国际(Mentor)和SiFive等。

CHIPS联盟藉由提供硅基元件和FPGA的开源硬体设计,希望能够创造开放合作的开发环境来降低研发成本,而小芯片概念的初衷,也呼应了半导体供应链在共同面对开发成本与技术挑战时的迫切需求。「业界对小芯片的开发需求来自几个面向,包含标准化的介面,更确切的说,是一个标准化的实体层,而且必须利用特定的制程或封装技术来展示应用范例,要做到这些,我们也需要EDA生态系的支援。」CHIPS联盟执行长Rob Mains表示。

SiFive旗下负责ASIC与IP开发的事业单位OpenFive也推出HBM/D2D解决方案,近期更宣布,利用其HBM3与D2D介面IP、SiFive的32位元Risc-V核心以及台积电5nm制程,已成功完成芯片设计(tape-out),能够打造高效能的小芯片,将多个芯片整合,或利用中介层完成2.5D封装,应用锁定高效能运算、AI运算、网路或储存等热门应用。

可以想见,小芯片从FPGA、CPU将一路扩展至GPU、APU等元件开发上,近年屡次以创新技术大举推出物美价廉处理器竞品的AMD也是小芯片的主要开发商,其采用Zen 2架构的EPYC处理器就成功地把负责主要运算和处理其他连接或控制功能的元件区隔开来,整合7nm与14nm各自的效能与成本优势。下一步他们更将进击GPU领域,除了要让小芯片之间的连接设计能确保记忆体的资料同步,与CPU连接的Pipeline技术也会是未来关注的重点。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2669内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备|封测

|射频|存储|美国|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie