一文看懂TSV

来源:内容由半导体行业观察(ID:icbank) 转载自迈铸半导体 ,作者: Dr. Gu, 谢谢。

在

2000

年的第一个月,

Santa Clara University

的

Sergey Savastiou

教授在

Solid State Technology

期刊上发表了一篇名叫

《Moore’s Law – the Z dimension》

的文章。这篇文章最后一章的标题是

Through-Silicon Vias

,这是

Through-Silicon Via

这个名词首次在世界上亮相。这篇文章发表的时间点似乎也预示着在新的千禧年里,

TSV

注定将迎来它不凡的表演。

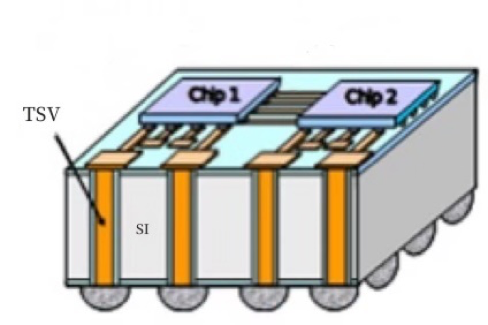

TSV示意图

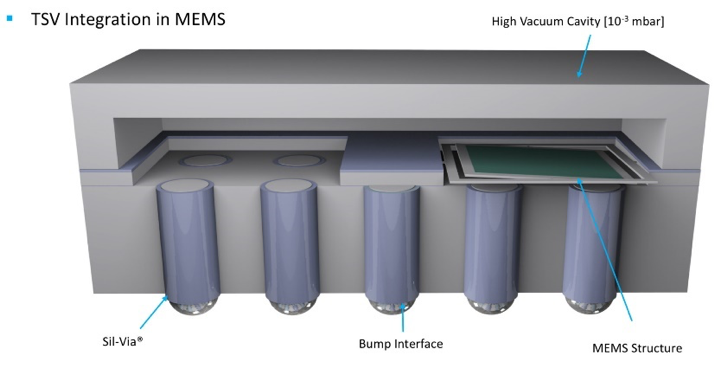

TSV ,是英文 Through-Silicon Via 的缩写,即是穿过硅基板的垂直电互连。

如果说

Wire bonding

(引线键合)和

Flip-Chip

(倒装焊)的

Bumping

(凸点)提供了芯片对外部的电互连,

RDL

(再布线)提供了芯片内部水平方向的电互连,那么

TSV

则提供了硅片内部垂直方向的电互连。

作

为唯一的垂直电互连技术,

TSV

是半导体先进封装最核心的技术之一。

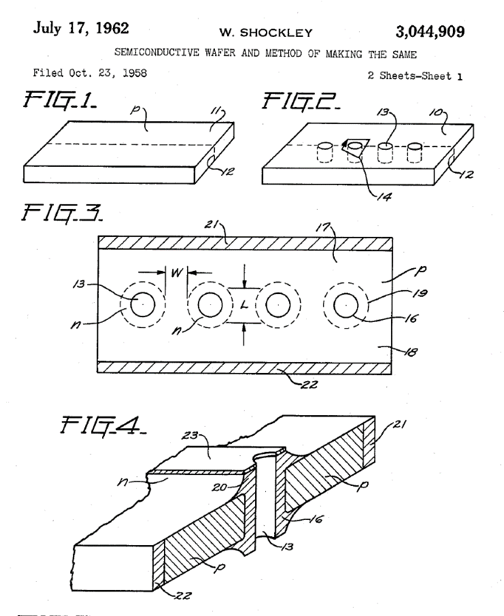

与集成电路一起诞生的垂直互联

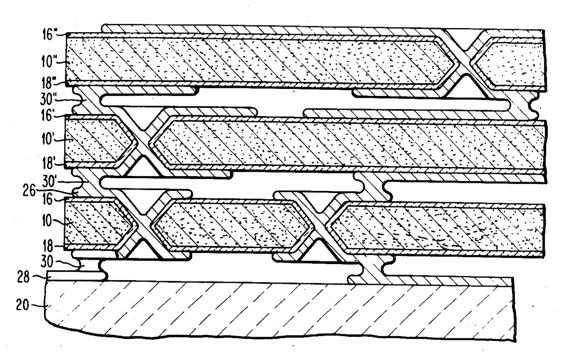

技术的突破

走向商用

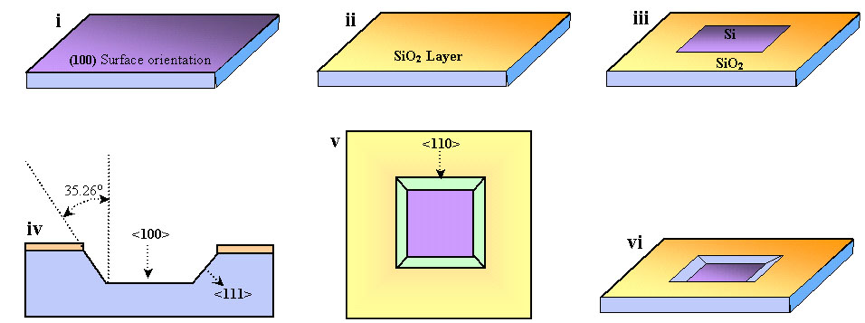

不走寻常路的Sil - Via

结 语

References

【1】Anisotropic Etching for Forming Isolation Slots in Silicon Beam-Leaded Integrated Circuits, H.A. Waggener, IEEE TRANSACTION OF ELECTRON DEVICES, JUNE 1968.

【2】Three-Dimensional Integrated Circuit (3D IC) Key Technology: Through-Silicon Via (TSV), Wen-Wei Shen and Kuan-Neng Chen, Nanoscale Research Letters (2017) 12:56

【3】JP S59 22954 & JP S63 156348

【4】 High aspect ratio silicon etch: A review, Banqiu Wua), Ajay Kumar, and Sharma Pamarthy, Journal of Applied Physics 108, 051101 (2010); https://doi.org/10.1063/1.3474652.

【5】 METHOD OF MANUFACTURING SEMCONDUCTOR DEVICES, Patent No. 3,661,727.

【6】E.Spiller, R.Feder, J.Topalian, E.Castellani, L.Romankiw and M.Heritage, “X-ray Lithography for Bubble Devices,”Solid State Technol.,April1976,pp62-68.

【7】E.W.Becker, W.Ehrfeld, D.Munchmeyer, H.Betz, A.Heuberger, S.Pongratz, W.Glashauser, H.J.Micheland V.R.Siemens, “Production of Separate Nozzle Systems for Uranium Enrichment by a Combination of X-ray Lithograohy and Galvanoplastics,” Naturwissenschaften,vol.69,pp.520-523,1982.

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3035内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔在研究哪些“超”前沿新技术?

- 2 Mentor线上讲堂 | 如何使用 HLS 来优化 AI/ML、视觉和智能 IoT 应用的性能和功耗/能耗

- 3 2024北京车展黑芝麻智能揭晓武当系列项目落地和生态链合作新图景

- 4 43亿元,美光西安封装和测试工厂正式破土动工!