国产存储量产前,要重视这个问题

来源:内容来自申万宏源,谢谢。

中兴事件的“禁售”危机虽然解除,但也让国人充分认识到了我国半导体产业发展的短板所在,高端芯片被海外“扼住咽喉”,成为我国高新产业发展的阿克琉斯之踵。

我国集成电路市场稳步增长, 严重依赖进口。 2017 年我国集成电路市场规模达到1.67 万亿元,同比增长 17.5%,但是国内集成电路市场主要依赖进口, 进口额达到 2601亿美元, 贸易逆差达到 1932 亿美元。 近年来国家尤其重视对集成电路国产化的发展, 国务院在《中国制造 2025》报告里提出到 2020 年中国芯片自给率达到 40%, 2025 年达到507%,今年《政府工作报告》又将集成电路列入实体经济发展首位。

2018 年 3 月 30 日,财政部等三部门发布《关于集成电路生产企业有关企业所得税政策》的通知, 对满足要求的集成电路企业实行税收优惠减免政策,此外为推动集成电路及相关配套产业国产化,国家成立集成电路产业大基金,截至 2017 年底,大基金累计有效决策投资 67 个项目,累计项目承诺投资额 1188 亿元,实际出资 818 亿元,分别占一期募资总额的 86%和 61%,投资项目覆盖集成电路设计、制造、封装测试、装备、材料、生态建设等各环节,实现了产业链上的完整布局。

我国集成电路的市场规模

大基金二期拟募集 1500 -2000 亿元人民币,有望于 2018 年下半年投资运行。 作为使用最为普遍的一种高端通用芯片,存储器在集成电路细分市场中规模居首。随着“大数据”时代的来临,云计算、互联网为使用者带来便利的同时,也带来了信息安全方面的潜在风险。 由于越来越多经济、社会、科技、军事等信息和资源被存储器储存收集,极易被窃取和利用, 存储器作为信息存储的核心载体,其安全性更受到高度重视。 因此存储芯片国产化已上升为涉及国家信息安全的战略地位。

2017 年我国集成电路贸易逆差达 1932 亿美元

从海外半导体产业发展路径看,存储器产业发展成为其实现国家半导体产业崛起的切入点。 1957 年 Intel 从存储器 1103 芯片起家, 1971 年 Intel 推出第一代 4004 CPU,Intel 从存储器技术积累到处理器演进的过程证明了技术路线可行性。此后,韩国三星、日本东芝等国际知名半导体企业从存储器产品线成功发展到处理器,带动了日韩半导体产业的崛起。

自上世纪 80 年代至本世纪初,存储器产业先后由美国转移至日本,日本转移至韩国,而后转移到我国台湾地区,存储器产业的每次转移都相继带动了这些地区集成电路产业乃至电子信息产业的蓬勃发展,证明了存储器的技术积累对于整个半导体产业发展的重要性。

目前我国加大了对存储器产业的投入,重点推进以长江存储(武汉新芯)、合肥长鑫、福建晋华为代表的存储器项目, 2019 年有望成为量产元年。 其中武汉新芯在国家大基金和湖北省、武汉市等地方投资基金共同出资 240 亿美元的大力支持下,筹划国内最大规模存储器生产基地的建设,并迅速推进 3D NAND Flash 工艺研发。 2018 年 4 月 11日,该项目生产机台正式进场安装, 长江存储已经获得第一笔 32 层 3D NAND 芯片订单,数量达到 10,776 颗,明年将进入 128Gb 的 3D NAND 在 64 层技术的研发。

同时近日多台ASML 光刻机运抵国内, 5 月 19 日长江存储首台光刻机运抵武汉; 5 月 21 日,华力二期(华虹六厂)首台光刻机进场; 中芯国际也已向 ASML 订购一台 EUV 光刻设备,预计 2019 年交付。 光刻机的进场,标志着国内晶圆厂从厂房建设进入到量产准备阶段。 2019 年将成为国内存储器量产元年,我国集成电路产业也将进入新的发展阶段。随着下游产业的发展,上游前驱体等相关电子材料也将迎来发展机会,率先切入产业链的企业将形成先发优势,充分享受产业上升期的市场红利。

中国大陆正在兴建的存储器芯片生产线

存储器推动半导体销售额高增,市场主要被日韩垄断

存储器是具备可以储存图像数据或文字数据、程序等信息,在必要时取出的功能的器件。从半导体存储器技术的分类来看,目前 DRAM 和 NAND 闪存的总产值占全球存储器产业的 95%,其中 DRAM 是动态随机存取存储器,数据只能保持很短的时间, 并且关机后就会丢失,电脑上 4G/8G/16G 内存采用的就是 DRAM,而 NAND Flash 闪存是一种非易失性存储技术,即断电后仍能保存数据,如手机 16G/32G/64G 的闪存和电脑上固态硬盘采用的是 NAND Flash。

半导体存储器的分类

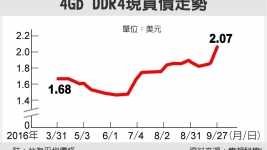

半导体销售创纪录,存储器市场成最大主要推动力。 2014-2016 年全球半导体销售额基本变化不大,而 2017 年半导体销售额同比增长 21.6%,达到创纪录的 4122 亿美元,这主要得益于存储器市场的高速增长。 2016 年下半年开始, 由于存储器市场供需格局反转,供不应求的局面逐渐愈演愈烈,产品价格持续上涨。 受此影响, 2017 年存储器市场销售额大幅增长 61.5%,达到 1240 亿美元,其中 DRAM 销售增长 76.3%至约 728 亿美元,NAND flash 增长 42.9%至 492 亿美元。

2017 年全球半导体销售额同比增长 21.6%

近年来,随着数据中心、 移动、汽车、物联网等领域的发展带动存储需求的不断增长,美光认为 2017 到 2021 年间,市场对 DRAM Bit 需求量年复合增长将达到 20%,其中移动和服务器市场为主要推动力,对 NAND Flash Bit 需求量的年复合增长将高达 40-50%,其中SSD 是最大的推动力,其次为移动市场。对于移动市场,随着手机 APP、游戏、视频、拍照等应用的增加,美光认为到 2021 年 DRAM 平均容量需求将接近 5GB,高端旗舰机达到 12GB;对 NAND Flash 平均容量达到 140GB,高端旗舰机将达到 1TB。

DRAM 和 NAND 未来需求将保持快速增长

全球存储器市场主要被日韩企业垄断。韩国三星在 DRAM 和 NAND 领域分别占有 40%以上的市场份额,处于绝对龙头地位,韩国海力士、日本东芝等企业也占有重要地位, 两家企业分别占据 DRAM 和 NAND 市场份额的第二位置。

全球DRAM的市场规模

全球NNAD的市场规模

3D NAND Flash 优势突出,逐步加快对 2D NAND 替代

2D NAND Flash 受制物理极限,厂商技术转向 3D NAND。 3D NAND Flash 随着对存储器器容量需求和成本要求的不断提升, NAND 的制程工艺不断进步,从早期的 50nm 发展到目前主流的 15/16nm, 产品品种由 SLC 向 MLC 过渡,以及发展到 TLC。

然而 NAND 闪存与处理器不同的是,先进工艺在容量提升、成本降低的同时,闪存的可靠性及性能都在下降, 因此厂商不得不采取额外手段进行弥补, 这样变相提高了制造成本, 因此传统的 2D NAND Flash存在其物理极限, 其单位面积存储容量很难继续提高,同时当达到某个性能和成本的平衡点之后, 制程工艺已经无法继续带来优势。 为了突破平面 2D NAND Flash 的物理极限,三星、海力士、东芝等厂商开始将技术转向 3D,开发 3D NAND Flash。

全球主要存储器厂商主流工艺

3D NAND Flash 在提升存储密度同时可有效降低功耗及成本。 3D NAND Flash 区别于传统 2D 平面的闪存,采用的是 3D 立体的堆叠方式, 简单意义上讲,即将原来 NAND Flash 中 2 维平面横向排列的串联存储单元改为垂直排列。 如果把 2D NAND Flash 看作一层的平房,3D NAND Flash 即是高楼大厦, 通过增加立体硅层的堆叠层数,既提高单位面积存储密度,又保障了存储单元性能,同时可以将成本控制在较低水平。

3D NAND 比 20 纳米级产品的容量密度高,读写速度快,耗电量节省,采用 3D NAND 闪存存储器的固态硬盘(SSD)其电路板面积也较小。 3D 技术不仅使产品性能至少提升 20%,而且功耗可以降低 40%以上。 目前东芝的 15nm NAND容量密度为 1.28Gb/mm²,而三星 32层堆栈的 3D NAND可以轻松达到 1.87Gb/mm²,48 层堆栈的甚至可以达到 2.8Gb/mm²。

闪存制造工艺的 2D 平面向立体 3D 发展示意图

2016 年开始 3D NAND FLASH 逐步对 NAND FLASH 进行替代。 自 2013 年 8 月三星率先宣布成功推出 3D NAND 之后,在技术上每年都会前进一步,由 24 层、 32 层、 48 层, 目前已进入到 64 层和 72 层。 据 AMAT 数据,全球晶圆厂就支出成长率来看,最大成长动力来自 3DNAND。 3D NAND 最大的需求来源于智能移动终端和电脑 SSD 需求, 随着 4K、 VR、 AR、 AI、5G 等新兴技术的不断推出, 物联网时代的来临对存储器容量及读写速度要求越来越高。 未来多家厂商逐渐量产, 3D NAND 将逐渐成为 NAND 闪存主流。 根据 IBS 预测 3D NAND 市场将由 2015 年 7.1%提升至 2025 年的 98.2%,市场规模将达到 685 亿美元。目前 3D NAND 市场基本被三星、东芝、美光、 SK 海力士等垄断。

物联网终端需求将是几何级数上升

大容量存储对应高深宽比制造要求, ALD 沉积工艺更具优势

薄膜沉积是集成电路制造过程中必不可少的环节,传统的薄膜沉积工艺主要有 PVD、 CVD 等气相沉积工艺:

PVD(物理气相沉积): 在真空条件下,采用物理方法,将材料源(固体或液体) 表面 气化成气态原子、分子或部分电离成离子,并通过低压气体(或等离子体)过程,在基体表面沉积具有某种特殊功能的薄膜的技术。 PVD 主要方法包括真空蒸度、溅射镀膜等, 不仅可沉积金属膜、合金膜, 还可以沉积化合物、陶瓷、半导体、聚合物膜等,所涉及材料包括所有固体(C、 Ta、 W 困难)、卤化物和热稳定化合物。

CVD(化学气相沉积): 主要是利用含有薄膜元素的一种或几种气相化合物或单质、在衬底表面上进行化学反应生成薄膜的方法。 CVD 法可制作薄膜材料包括碱及碱土类以外的金属(Ag、 Au 困难)、碳化物、氮化物、硼化物、氧化物、硫化物、硒化物、碲化物、金属 化合物、合金等。

随着集成电路集成度越来越高,尺寸越来越小,高介电常数(high k)栅介质逐渐替代传统的氧化硅栅,同时高宽比越来越大,对沉积技术的台阶覆盖能力提出了更高的要求,因此 ALD 作为能够满足以上要求的新型沉积工艺已被越来越多的采用:

ALD(原子层沉积) : 可以理解为一种变相的 CVD 工艺,通过将气相前驱体脉冲交替地 通入反应器并在沉积基体上化学吸附并反应形成沉积膜的一种方法。与传统 CVD 不同的是,ALD 在沉积过程中, 反应前驱体是交替沉积, 新一层原子膜的化学反应是直接与之前一层相关联的,这种方式使每次反应只沉积一层原子。 ALD 已沉积材料包括金属、氧化物、碳(氮、硫、硅)化物、各类半导体材料和超导材料等。

ALD沉积材料

ALD 相比传统的 PVD 和 CVD 等淀积工艺, 充分利用表面饱和反应,天生具备厚度控制和 高度的稳定性能,对温度和反应物通量的变化不太敏感。 因此 ALD 法沉积的薄膜兼具高纯度和高密度,既平整又具有高度的保型性,即使对于纵宽比高达 100:1 的结构也可实现良好的阶梯覆盖。 而 ALD 此前主要缺点在于沉积速度较慢,大约 1 Å/min,但是随着目前沉积薄膜层厚度要求越来越薄,这一缺点的影响已不再成为问题。 ALD 开始在栅氧化层,扩散阻挡层和存储器结构中的电极薄膜层应用越来越广泛。

PVD、 CVD、 ALD 工艺特性比较

对于 ALD 工艺,前驱体的选择通常需要满足以下要求:(1) 在沉积温度下具有足够的 蒸汽压,以保证其能充分覆盖基底材料表面;(2)良好的热稳定性和化学稳定性,在沉积温度下不会发生自分解;(3)高反应性,保证其在基底表面迅速发生化学吸附,或与材料表面基团快速发生有效的反应,从而使表面膜具有高纯度;(4)反应副产物对基底和表面膜没有腐蚀性;(5)材料来源广泛, 低毒性。

常用的 ALD 前驱体包括非金属前驱体和金属前驱体。 非金属前驱体如卤化物(SiCl4、AlCl3等)、氮化物(NH3、(CH3)NNH2、BuNH2等),金属前驱体如烷基前驱体(Ga(CH3)3、Mg(C2H5)2)、 β-二酮前驱体(La(thd)3、Ca(thd)2)、醇盐前驱体(Ta(OC2H5)5、 Zr[(OC)(CH3)3]4)、烷基胺及硅胺基前驱体(Ti[N(C2H5CH3)2]4、 Pr[N(SiMe3)2]3) 等等。

3D NAND 的制造工艺十分复杂,主要包括高深宽比的沟开挖(High aspect ratio trenches)、在源与漏中不掺杂(No doping on source ordrain)、完全平行的侧壁(Perfectly parallel walls)、众多级的台阶(Tens of stairsteps)、在整个硅片面上均匀的淀积层(Uniform layer across wafer)、一步光刻楼梯成形(Single-Lithostairstep)、硬掩模刻蚀(Hard mask etching)、通孔工艺(Processing inside of hole)、孔内壁淀积工艺(Deposition on hole sides)、多晶硅沟道(Polysilicon channels)、电荷俘获型存储(Charge trap storage)、多种材料的通孔刻蚀(Etch through varying materials)、复合多层膜沉积(Deposition of tens of layers)等。

3D NAND 基本工艺流程

由于 3D NAND 复杂结构需要制造高的纵深比,相关流程包括叠层沉积、高深宽比通道孔蚀刻、字线金属化、阶梯蚀刻、高深宽比狭缝蚀刻,以及阶梯接触线成型等。 其中叠层沉积和自线金属化对沉积工艺提出了极高要求,在这方面 ALD 工艺比传统 CVD 及 PVD 工艺更具优势。

3D NAND 结构及关键沉积、蚀刻流程

ALD 工艺可有效减小应力。 3D NAND 堆叠存储单元的制造环节起始于交替薄膜沉积, 精 确控制每层薄膜厚度的均一性至关重要, 晶圆翘曲和局部薄膜应力直接影响到光刻叠对精度, 薄膜的厚度和重复性则影响存储单元的有效体积和光刻/蚀刻表现的一致性。因此,薄膜应力控制和良好的均匀性对晶圆良率十分关键。 同时,在采用置换栅极工艺的 3D NAND中,同层中存储单元的导线连接靠钨填充实现, 传统化学 CVD 钨薄膜具有高伸张应力,会导致晶圆翘曲,同时工艺带来的氟元素会扩散到邻层,造成缺陷并影响良率。 而采用低氟钨(LFW) 的 ALD 工艺可以制造出更光滑的表面形貌,更紧密地贴合每个填充层,从而减小沉积流程产生的应力。 相比于传统 CVD 钨沉积技术, ALD 低氟钨技术可降低一个数量级以上的应力(GPa→hMPa)、 99%的氟含量以及 30%以上的电阻率。

ALD 沉积薄膜均匀性更高,产生的应力最小

除了有效控制应力, ALD 具有更好的台阶覆盖能力,可满足 3D NAND 制造过程中高深 宽比的要求。 随着 3D NAND 层数的增加,孔道的深宽比也不断加大,制造中需要在深宽比100: 1 的孔道中纵向和横向高 K 介质(Al2O3)、钛阻挡层(Ti/TiN)等物质。 由于 ALD 沉积过程可有效控制薄膜的厚度和均匀性,因此可以实现高深宽比孔道的均匀覆盖,而 PVD 和CVD 对于高深宽比的台阶则无法实现均匀覆盖,约接近台阶顶部厚度越厚,若台阶的深宽比过高,可能会造成顶部开口堵塞。

PVD 等方法通常无法实现高深宽比的均匀覆盖

不仅 3D NAND 如此, 平面 DRAM 最重要也最艰难的挑战,是储存电容的高深宽比。 储存电容的深宽比会随着元件制程微缩而呈倍数增加,导致平面 DRAM 的制程微缩会越来越困难,因此 ALD 工艺在平面 DRAM 及 NAND 中也有重要应用。

DRAM 制程越窄,深宽比越高

存储产业驱动前驱体市场不断扩大, 3D 结构刺激需求增长

前驱体是半导体薄膜沉积工艺的主要原材料。 IC 前驱体可以概括为:应用于半导体生产制造工艺,携有目标元素,呈气态或易挥发液态,具备化学热稳定性,同时具备相应的反应活性或物理性能的一类物质。在包括薄膜、光刻、互连、掺杂技术等的半导体制造过程中,前驱体主要应用于气相沉积(包括 PVD、 CVD 及 ALD),以形成符合半导体制造要求的各类薄膜层。 半导体前驱体可分为: TEOS(正硅酸乙酯)、硼磷(B、 P)掺杂剂、金属前驱体、高 k 前驱体、低 k 前驱体等。

半导体用前驱体材料

随下游逻辑、存储等芯片产业发展,前驱体总体市场规模将保持快速增长。 根据日本富士经济数据,全球前驱体销售规模在 2014 年约 855 亿日元左右(约 7.5 亿美元),同比增长 28.81%;预计 2019 年达到 1358 亿日元(约 12.0 亿美元) ,CAGR 达到 10%。

全球半导体前驱体销售收入(百万日元)

根据 SEMI 旗下的 Chemical and Gases Manufacturers Group 推荐的半导体材料市场调研公司 Techcet 的报告, 由于复杂的 3D 结构极大的激发了对高 k 沉积制程的需求,带动高 k 及金属前驱体市场快速增长,2015 年用于 ALD/CVD的高 k 及金属前驱体市场规模为 1.85亿美元,2019 年增长为 3.25 亿美元, CAGR 约 15%。

ALD/CVD 的高 k 及金属前驱体迎来快速增长

今天是《半导体行业观察》为您分享的第1621期内容,欢迎关注。

★ 倪光南往事

★ 可怕的三星半导体

关注微信公众号 半导体行业观察(ID:icbank) ,后台回复以下关键词获取更多相关内容

华虹 | 摩尔定律 | 材料 | 面板 | 晶体管 | 开源 | 韦尔股份 | 封装 | 展会

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!

点击阅读原文了解摩尔精英

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 2 研发收关:进迭时空高性能处理器核X100产品发布会震撼来袭

- 3 MediaTek天玑汽车平台推动汽车产业加速迈入AI时代,3nm旗舰座舱平台亮相

- 4 国内首颗,精准纠错!德明利TWSC2985系列:支持4K LDPC技术的存储芯片